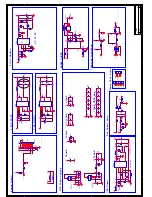

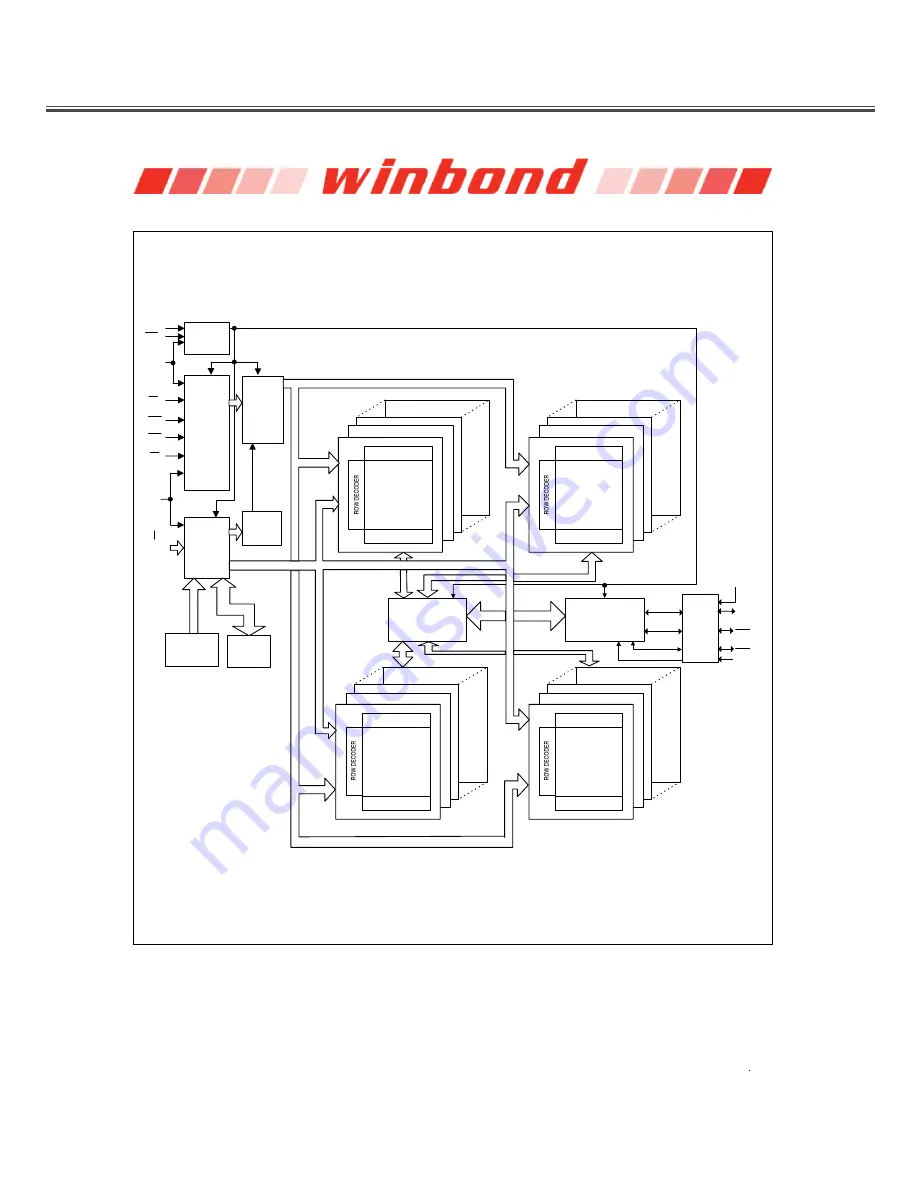

IC Block Diagram

-

31

-

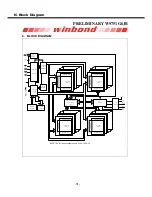

PRELIMINARY W9751G6JB

6.

BLOCK DIAGRAM

CKE

A10

DLL

CLOCK

BUFFER

COMMAND

DECODER

ADDRESS

BUFFER

REFRESH

COUNTER

COLUMN

COUNTER

CONTROL

SIGNAL

GENERATOR

MODE

REGISTER

COLUMN DECODER

SENSE AMPLIFIER

CELL ARRAY

BANK #2

COLUMN DECODER

SENSE AMPLIFIER

CELL ARRAY

BANK #0

COLUMN DECODER

SENSE AMPLIFIER

CELL ARRAY

BANK #3

DATA CONTROL

CIRCUIT

DQ

BUFFER

COLUMN DECODER

SENSE AMPLIFIER

CELL ARRAY

BANK #1

NOTE: The cell array configuration is 8192 * 1024 * 16

A0

A9

A11

A12

BA1

BA0

CS

RAS

CAS

WE

CLK

CLK

PREFETCH REGISTER

ODT

CONTROL

DQ0

|

DQ15

LDQS

LDQS

UDQS

UDQS

LDM

UDM

ODT

Summary of Contents for 8M29B

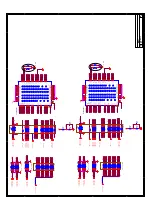

Page 3: ... 3 LCD 8M29B chassis ...

Page 5: ...For 42LED For 42LED 5 8 8 10 15 9800 12500 12500 266 276 9800 280 290 6500 313 329 ...

Page 6: ...40 40 3 2 1 4 2 50 0 5 80 40 12000 6 24 6 ...

Page 8: ... 8 4 ...

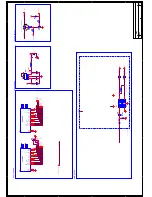

Page 19: ...IC Block Diagram 19 LM4558 MP1482DS BS IN SW GND SS EN COMP FB 1 2 3 4 8 7 6 5 TOP VIEW ...

Page 20: ...IC Block Diagram 20 MST6M20S LF ...

Page 23: ...IC Block Diagram 23 EN25F32 Figure 2 BLOCK DIAGRAM ...

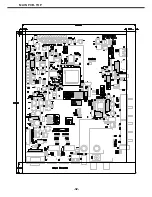

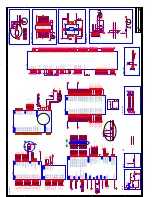

Page 32: ...MAIN PCB TOP 32 ...

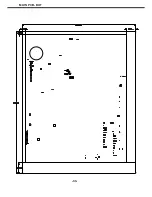

Page 33: ...MAIN PCB BOT 33 ...