19

AK - 45

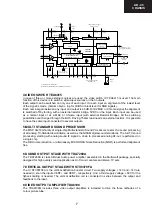

CHASSIS

Memory

• Non-multiplexed 8-bit data and 16 … 20-bit address bus (ROMless Version)

• Memory banking up to 1Mbyte (ROMless version)

• Up to 128 Kilobyte on Chip Program ROM

• Eight 16-bit data pointer registers (DPTR)

• 256-bytes on-chip Processor Internal RAM (IRAM)

• 128bytes extended stack memory.

• Display RAM and TXT/VPS/PDC/WSS-Acquisition-Buffer directly accessible via MOVX

• UP to 16KByte on Chip Extended RAM (XRAM) consisting of;

- 1 Kilobyte on-chip ACQ-buffer-RAM (access via MOVX)

- 1 Kilobyte on-chip extended-RAM (XRAM, access via MOVX) for user software

- 3 Kilobyte Display Memory

Display Features

• ROM Character Set Supports all East and West European Languages in single device

• Mosaic Graphic Character Set

• Parallel Display Attributes

• Single/Double Width/Height of Characters

• Variable Flash Rate

• Programmable Screen Size (25 Rows x 33...64 Columns)

• Flexible Character Matrixes (HxV) 12 x 9...16

• Up to 256 Dynamical Redefinable Characters in standard mode; 1024 Dynamical Redefinable

Characters in Enhanced Mode

• CLUT with up to 4096 colour combinations

• Up to 16 Colours per DRCS Character

• One out of Eight Colours for Foreground and Background Colours for 1-bit DRCS and ROM

Characters

• Shadowing

• Contrast Reduction

• Pixel by Pixel Shiftable Cursor With up to 4 Different Colours

• Support of Progressive Scan and 100 Hz.

• 3 X 4Bits RGB-DACs On-Chip

• Free Programmable Pixel Clock from 10 MHz to 32MHz

• Pixel Clock Independent from CPU Clock

• Multinorm H/V-Display Synchronization in Master or Slave Mode

Acquisition Features

• Multistandard Digital Data Slicer

• Parallel Multi-norm Slicing (TTX, VPS, WSS, CC, G+)

• Four Different Framing Codes Available

• Data Caption only Limited by available Memory

• Programmable VBI-buffer

• Full Channel Data Slicing Supported

• Fully Digital Signal Processing

• Noise Measurement and Controlled Noise Compensation

• Attenuation Measurement and Compensation

• Group Delay Measurement and Compensation

• Exact Decoding of Echo Disturbed Signals

Ports

• One 8-bit I/O-port with open drain output and optional I

2

C Bus emulation support (Port 0)

• Two 8-bit multifunction I/O-ports (Port 1, Port 3)

• One 4-bit port working as digital or analog inputs for the ADC (Port 2)

• One 2-bit I/O port with secondary functions (P4.2, 4.3, 4.7)

• One 4-bit I/O-port with secondary function (P4.0, 4.1, 4.4) (Not available in P-SDIP 52)

13.11.MC44608

13.11.1.Description

The MC44608 is a high performance voltage mode controller designed for off–line converters. This high

voltage circuit that integrates the start–up current source and the oscillator capacitor, requires few

Summary of Contents for C-2890EES

Page 7: ...7 C 2890EES CHASSIS LAYOUT Mother Unit CRT Unit Control Panel Unit ...

Page 69: ...53 AK 45 CHASSIS 14 6 GEOMETRY ADJUSTMENT 4 3 FORMATS 4 3 MODE 16 9 MODE ...

Page 70: ...54 AK 45 CHASSIS 16 9 FORMATS AUTO MODE ...

Page 71: ...55 AK 45 CHASSIS REGULAR MODE ...

Page 72: ...56 AK 45 CHASSIS ZOOM 14 9 MODE ...

Page 73: ...57 AK 45 CHASSIS ZOOM 16 9 MODE ...

Page 74: ...58 AK 45 CHASSIS SUBTITLE ZOOM MODE ...

Page 75: ...59 AK 45 CHASSIS FULL MODE ...

Page 76: ...60 AK 45 CHASSIS PANORAMIC MODE ...

Page 86: ...70 AK 45 CHASSIS 1 I H G F E D C B A 2 3 4 5 6 7 16 7 Schematic Diagram of CRT Socket Circuit ...

Page 91: ...75 AK 45 CHASSIS Notes ...