LC-32LE40E-LC-42LE40E

58

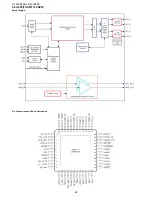

2.6 U4051(NAND256W3A2BN6E)(for 32”)

General Description

The NAND Flash 528 Byte/ 264 Word Page is a family of non-volatile Flash memories that uses the Single Level Cell (SLC) NAND cell technology.

It is referred to as the Small Page family. The devices range from 128Mbits to 1Gbit and operate with either a 1.8V or 3V voltage supply. The size of

a Page is either 528 Bytes (512 + 16 spare) or 264 Words (256 + 8 spare) depending on whether the device has a x8 or x16 bus width. The address lines

are multiplexed with the Data Input/Output signals on a multiplexed x8 or x16 Input/Output bus. This interface reduces the pin count and makes it possible

to migrate to other densities without changing the footprint. Each block can be programmed and erased over 100,000 cycles. To extend the lifetime of

NAND Flash devices it is strongly recommended to implement an Error Correction Code (ECC). A Write Protect pin is available to give a hardware

protection against program and erase operations. The devices feature an open-drain Ready/Busy output that can be used to identify if the Program/

Erase/Read (P/E/R) Controller is currently active. The use of an open-drain output allows the Ready/Busy pins from several memories to be connected

to a single pull-up resistor. A Copy Back command is available to optimize the management of defective blocks. When a Page Program operation fails, the

data can be programmed in another page without having to resend the data to be programmed. The devices are available in the following packages:

■

TSOP48 12 x 20mm for all products

■

USOP48 12 x 17 x 0.65mm for 128Mb, 256Mb and 512Mb products

■

VFBGA55 (8 x 10 x 1mm, 6 x 8 ball array, 0.8mm pitch) for 128Mb and 256Mb products

■

VFBGA63 (9 x 11 x 1mm, 6 x 8 ball array, 0.8mm pitch) for the 512Mb product

All devices have the Chip Enable Don't Care option, which allows the code to be directly downloaded by a microcontroller, as Chip Enable

transitions during the latency time do not stop the read operation. A Serial Number option, allows each device to be uniquely identified. The Serial Number

options is subject to an NDA (Non Disclosure Agreement) and so not described in the datasheet. For more details of this option contact your nearest ST

Sales office.

Features

■

HIGH DENSITY NAND FLASH MEMORIES

– Up to 1 Gbit memory array

– Up to 32 Mbit spare area

– Cost effective solutions for mass storage applications

■

NAND INTERFACE

– x8 or x16 bus width

– Multiplexed Address/ Data

– Pinout compatibility for all densities

■

SUPPLY VOLTAGE

– 1.8V device: VDD = 1.7 to 1.95V

– 3.0V device: VDD = 2.7 to 3.6V

■

PAGE SIZE

– x8 device: (512 + 16 spare) Bytes

– x16 device: (256 + 8 spare) Words

■

BLOCK SIZE

– x8 device: (16K + 512 spare) Bytes

– x16 device: (8K + 256 spare) Words

■

PAGE READ / PROGRAM

– Random access: 12

μ

s (3V)/15us (1.8V) (max)

– Sequential access: 50ns (min)

– Page program time: 200

μ

s (typ)

■

COPY BACK PROGRAM MODE

– Fast page copy without external buffering

■

FAST BLOCK ERASE

– Block erase time: 2ms (Typ)

■

STATUS REGISTER

■

ELECTRONIC SIGNATURE

■

CHIP ENABLE ‘DON’T CARE’

– Simple interface with microcontroller

■

SERIAL NUMBER OPTION

Summary of Contents for AQUOS LC-42LE40E

Page 6: ...LC 32LE40E LC 42LE40E 6 2 OPERATION MANUAL Remote Control ...

Page 7: ...LC 32LE40E LC 42LE40E 7 TV Front TV Side Rear ...

Page 11: ...LC 32LE40E LC 42LE40E 11 3 DIMENSIONS ...

Page 40: ...LC 32LE40E LC 42LE40E 40 ...

Page 62: ...LC 32LE40E LC 42LE40E 62 2 DETAILED ICS INFORMATION 3 1 U401 MT5366CAOU B Block Diagram ...

Page 63: ...LC 32LE40E LC 42LE40E 63 Pin Connections and Short Description ...

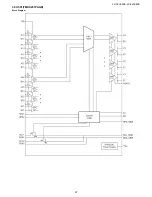

Page 67: ...LC 32LE40E LC 42LE40E 67 3 5 U501 TMDS251PAGR Block Diagram ...

Page 68: ...LC 32LE40E LC 42LE40E 68 Pin Connections and Short Description ...

Page 71: ...LC 32LE40E LC 42LE40E 71 3 7 U4053 ICL3232ECV Pin Connections and short description ...

Page 151: ...LC 32LE40E LC 42LE40E 151 2 CABINET PARTS LC 32LE40E ...