13

CHAPTER 1

Stepping through the sample application

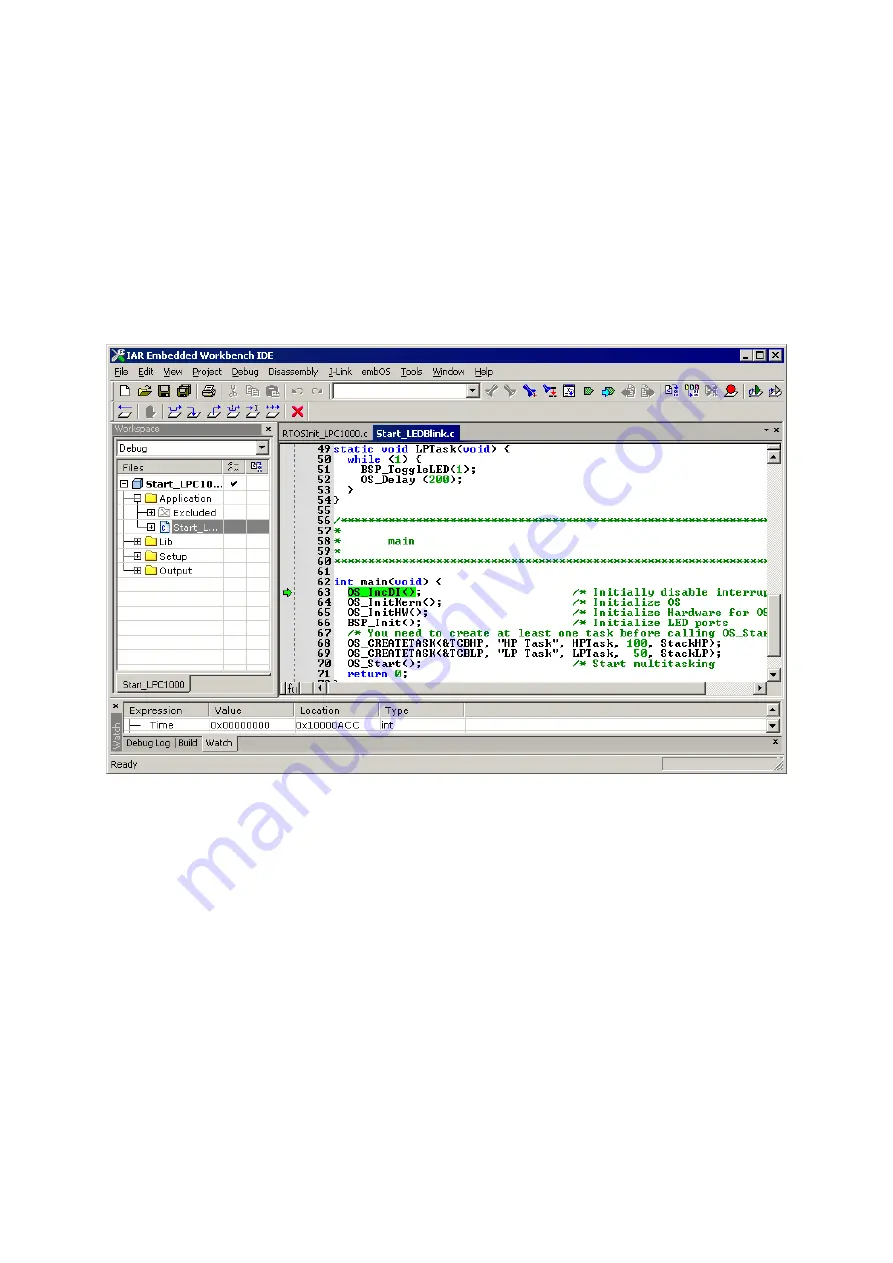

1.4 Stepping through the sample application

When starting the debugger, you will see the

main()

function (see example screen shot

below). The

main()

function appears as long as project option

Run to main

is selected,

which it is enabled by default. Now you can step through the program.

OS_Init()

is part of the embOS library and written in assembler; you can there fore only

step into it in disassembly mode. It initializes the relevant OS variables.

OS_InitHW()

is part of

RTOSInit.c

and therefore part of your application. Its primary

purpose is to initialize the hardware required to generate the system tick interrupt for

embOS. Step through it to see what is done.

OS_Start()

should be the last line in

main()

, because it starts multitasking and does not

return.

embOS-MPU for Cortex-M and IAR

© 2010-2020 SEGGER Microcontroller GmbH