Circuit Description

5-2

SF150T

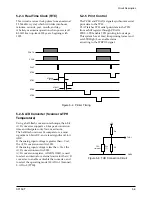

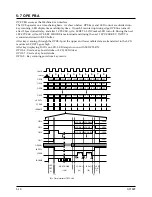

Figure 5-2: XFC Hardware Interface Signals

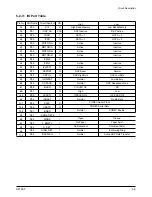

5-2-2 lExternal Chip Control

KS16118 internal logic generates chip select signals for both memory chips and peripherals.

To support external access, from one to three wait cycles can be inserted under program control during

external access.

A chip select signal line goes active (low) whenever its corresponding device is accessed over the external

interface. The peripheral addresses are located in data memory space.

/DMS : SRAM chip select active (low)

/PMS : EP-ROM chip select active (low)

/PCSn : Peripheral chip select active (low)

D0 - D7 : 8 bit data bus

A0 - A15 : address bus

5-2-3 System Clock

The 12 MHz internal system clock frequency is generated by dividing the 24 MHz clock.

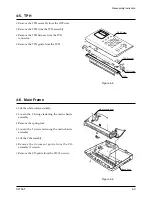

OPERATING

PANEL

PRINTER DATA

CONTROL AND

SENSORS

MOTOR

DRIVER

(MOTOR)

SCANNER

CONTROL

AND

PROCESSING

RTC

CRYSTAL

DATA

MEMORY

PROGRAM

MEMORY

GENERAL

PURPOSE I/ 0

OP00-OP06

LED_CTL

LCD_EN

OPI0-OPI3

STB 0-3

PDAT

PCLK

PLAT

THADI

SM0-SM3

MODE

SI

CLK1

Vin

+Vref

-Vref

XIN

XOUT

/DMS

/RD /WR

D0~D7

A0~A14

/RD

D0~D7

A0~A15

A16

/PMS

RESTOUT

/RESET

KS16118