XW-HTP550

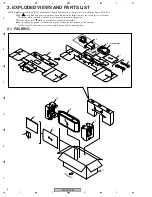

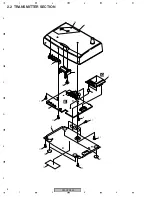

12

1

2

3

4

1

2

3

4

C

D

F

A

B

E

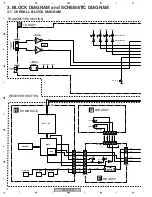

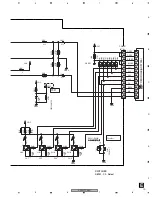

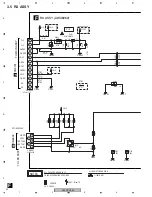

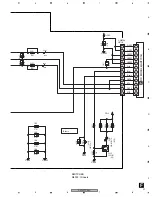

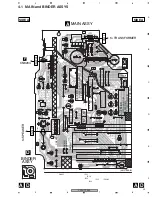

3. BLOCK DIAGRAM and SCHEMATIC DIAGRAM

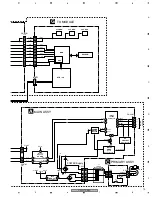

3.1 OVERALL BLOCK DIAGRAM

E

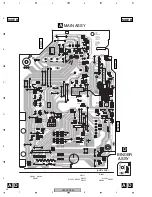

TX ASSY

B

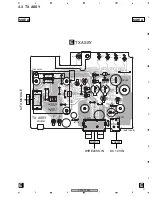

LED ASSY

F

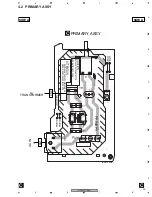

RX ASSY

H

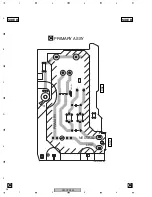

RX MODULE

TRANSMITTER SECTION

RECEIVER SECTION

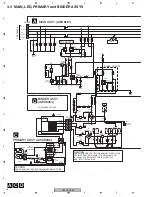

1

2

JA8202

ALC

L

R

Analog Audio

INPUT

DC IN

12V

JA8001

VD+5 VA+5

IC8051

NJM2374AM

5V REG.

IC8101

NJM12904M

V+5RF

3.3V REG.

3.3V REG.

2.8V REG.

POWER

ID Learn

ID Learn

TUNED

Ch.1

Ch.2

Ch.3

Ch.4

Q8501-Q8504

Ch. select

CN8203

(12P)

CN5901

(5P)

CN5902

(5P)

V+5RF

GNDD

LEDP

LEDTUN2

LEDTUN1

GNDD

V+5RF

ROUT

LOUT

2

12

10

1

7

8

6

2

12

10

1

7

8

6

1

2

3

4

1

2

3

4

L Ch

EEPROM

R Ch

VD+9

ANT2

BBIC

RF IC + PA

ID Learn

ID State

Sync

V+5RF

CN8204

(12P)

8

12

11

V+9

V+9

LOUT

ROUT

6

5

5

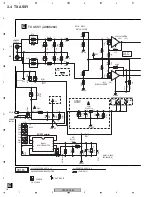

D8501-D8504

3

1

5

7

IC8003

REG 5V

NJM78M05FA

3

1

DAC