24

HTP-071

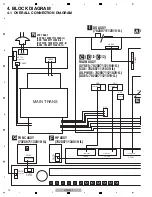

1

2

3

4

A

B

C

D

E

F

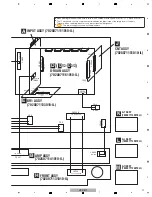

1

2

3

4

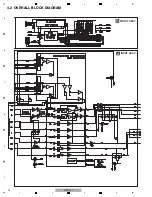

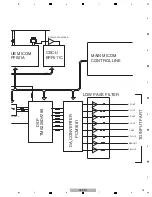

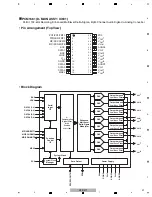

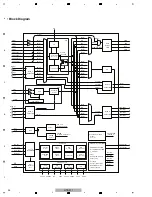

5.3 IC INFORMATION

J046941000010-IL (EP94A1K)(D-MAIN ASSY: IC200)

HDMI 1.3 4-In 1-Out Repeater with Audio Output

• Pin Arrangement (Top View)

• Block Diagram

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

2

66

65

1

RX

21+

RX21

-

AV

D

D

RX

1

1

+

R

X

11-

AV

S

S

AV

D

D

3

3

RX

0

1

+

R

X

01-

AV

S

S

RX

C

1

+

RX

C1

-

AV

D

D

PVDD

AV

S

S

RX

20+

RX20

-

AV

D

D

R

X

10+

R

X

10-

AV

S

S

AVD

D

33

RX

00+

RX

00-

AVS

S

RXC

0

+

RX

C0

-

AVD

D

PVDD

PVSS

AV

S

S

VDDE

RXC2-

AVDD

RX02-

RX02+

AVDD33

AVSS

RX12-

RX12+

AVDD

RX22-

RX22+

AVSS/PVSS

PVDD

AVSS

EXT_RES

AVSS

RXC2+

RXC3+

RXC3-

RX03+

AVDD33

AVSS

RX13-

RX13+

AVDD

RX23-

RX23+

AVSS

EXT_SWI

N

G

PVDD/AVDD

RX03-

AVSS

AV

S

S

TX

C

-

TX

C

+

AV

D

D

1

8

TX

0

-

TX

0

+

TX

1

-

TX

1

+

AVDD18

TX

2

-

TX

2

+

AV

S

S

AVDD33

VDD

N

C

DD

C3_

S

DA

D

DC3

_S

CL

DD

C2_SD

A

D

DC2

_S

CL

DD

C1_SD

A

D

DC1

_S

CL

VSSE

DS

D3R

DS

D3

L

IIS_SD3

IIS_SD2

IIS_SD1

I

N

Tb

EX

T_

RS

Tb

A_

MU

T

E

VSS

PVDD18

PH2

PH1

DDC0_SCL

DDC0_SDA

VSS

IIS_SD0

IIS_WS

IIS_SCK

MCLK

VSS

VSSE

SPDIF

VDD

VDD

VSS

VSS_PLL

PLL_XFC_A

VDD_PLL

VDDE

X_OUT

X_I

N

N

C

N

C

N

C

reserved

VDDE

VSS

MCU_SCL

MCU_SDA

VDD

VDD

VSS

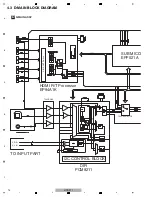

RX00+/-

RX10+/-

RX20+/-

RXC0+/-

DDC0_SDA

DDC0_SCL

RX01+/-

RX11+/-

RX21+/-

RXC1+/-

DDC1_SDA

DDC1_SCL

RX02+/-

RX12+/-

RX22+/-

RXC2+/-

DDC2_SDA

DDC2_SCL

HDMI

RX

Input

Port 1

4-

In 2-

Ou

t Switch

HDMI

RX

Input

Port 2

HDMI

RX

Input

Port 0

HDMI RX

HDCP Keys

IIS_SCK

IIS_WS

IIS_SD*/DSD*

MCLK

SPDIF

Registers

and

Control Logic

MCU_SCL

MCU_SDA

I

N

Tb

RX03+/-

RX13+/-

RX23+/-

RXC3+/-

DDC3_SDA

DDC3_SCL

HDMI

RX

Input

Port 2

EDID 3

EDID 2

EDID 1

EDID 0

HDCP RX

HDMI RX

HDC

P

RX

2-In

1-Out Switch

Port A

HDCP TX

HDMI TX

Primary RX

Secondary RX

TX0+/-

TX1+/-

TX2+/-

TXC+/-

Audio

Processor

IIS/SPDIF/DSD/HBR

OUT Processor

Summary of Contents for HTP-071

Page 9: ...9 HTP 071 5 6 7 8 5 6 7 8 A B C D E F ...

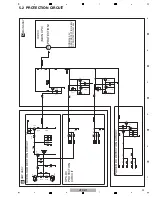

Page 12: ...12 HTP 071 1 2 3 4 A B C D E F 1 2 3 4 4 2 OVERALL BLOCK DIAGRAM H FRONT ASSY A INPUT ASSY ...

Page 89: ...89 HTP 071 5 6 7 8 5 6 7 8 A B C D E F C SIDE B CP1 CP3 CP5 CN1 CN3 ...

Page 93: ...93 HTP 071 5 6 7 8 5 6 7 8 A B C D E F D SIDE B CN600 CP104 ...