7

DV-505, DVL-909, DV-S9

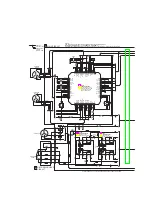

1.2.3 Tracking / Slider Servo

ATB: The tracking balance compensation is

achieved by outputting the offset from

the TBAL output at pin 46 of the digital

servo IC, and by biasing the charge pump

resistor for phase-difference error of

RFIC.

The difference is detected by processing

TE at pin 34 of IC 201 with an internal

digital equalizer.

TDO: In addition to the servo output, the low-

band components, such as the kick-brake

for jump, are added for TDO output.

SLDO: The low-band components of TE are

processed by the internal digital

equalizer, and deadband is added for

SLDO output. The offset voltage for

pickup movement is also included in the

SLDO output.

4

34

46

50

24

26

27

16

17

47

5

6

7

8

OEIC

PICKUP

IC101

RFIC

IC201

DIGITAL

SERVO IC

IC501

MECH.

CONTROL

IC151

DRIVER

• TRACKING / SLIDER SERVO

TE

TE RF

B1

B2

B3

B4

TRKG

COIL

TBAL

ADDRESS

&

BUS

TDO

19

SLDO

M

26

28

CP

SLDR

3

12

41

57

48

25

95

OEIC

IC101

RFIC

IC301

A/D

IC701

LSI II

IC201

DIGITAL

SERVO

IC161

DRV

• SPDL SERVO

RFO

RF

CLK

(27M)

8 bit

ATC

APC

AFC

ASC

V165

DUTY50

FG

VPWM

PPWM

RPWM

FPWM

31

50

32

RF

IC302

(1/2)

IC271

(2/2)

IC271

(1/2)

FG

SPDL +

SPDL -

SPDL

SPDO

(Base)

SPDO

(Compatible)

3

|

10

200

|

207

179

176

178

180

177

161 163 166 167

159

VCO

12

13

M

1.2.4 SPINDLE SERVO

For a CD, the RF signal output from pin 32 of the RF IC is converted

to binary in IC201. By comparing the binary value with the reference

CLK (clock), the SPDL ERR signal is output from pin 48.

For a DVD, the SPDL ERR signal is generated from the PWM signal

output from LSI-

ΙΙ

. Upon receiving this signal via pin 31, IC201

also outputs it from pin 48, switching from the CD SPDL ERR

signal.

Summary of Contents for DVL-K88

Page 33: ...DVL K88 33 ...

Page 84: ...84 DVL K88 8 PANEL FACILITIES AND SPECIFICATIONS FRONT PANEL ...

Page 85: ...85 DVL K88 DISPLAY WINDOW ...

Page 86: ...86 DVL K88 REMOTE CONTROL ...