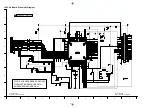

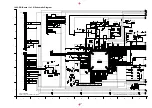

14.21. XV-Board Block Diagram

SBO1

SBI1

SPEN

SPCLK

SPPKTST

SPDATA7

XFERSTO

SBI1

SBO1

SPEN

SPCLK

SPPKTST

XFERSTO

CHCLK

CHVAL

CHSYNC

POWER

DR

DL

RESET

POWER

XCD1

XCD2

XWAIT

XIREQ

SPDATA7

XRST

X8003

X8006

41

43

DL(BS_L)

DR(BS_R)

XV01

96

88

105

MVCLK0

MHSYNC0

MVSYNC0

XRST

22

SBO1(SBI1)

18

SBI1(SBO1)

19

SUB 9V

13

SUB 9V

51

52

SUB 9V

53

SUB 9V

54

SUB 5V

57

SUB 5V

IC8023

PVIN

DC-DC CONV.3.3V

FB

2

3

INV

4

SUB 9V

VIN

SW

8

1

SUB 5V

FDC_A5V

A5V

SUB 9V

MVY0

MVY7

MVC0

MVC7

107

106

109

2

4

RESET

VDD

IC8043

OUT

2

1

RESET

VDD

IC8042

VOUT

VCC

1

VOUT

AVR +2.5V

IC8034

CTL

4

2

+2.5V

SUB 9V

3.3V

SUB 9V

TO DG22

MVY7

MVY0

MVC7

MVC0

MHSYNC0

MVSYNC0

MVCLK0

IEC_OUT

MVY0

MVC0

MVY7

MVC7

DY

DC

SDA1

SCL0

SDA0

SCL1

SCL0

SDA1

SDA0

SCL1

XRST

SBO1

SBI1

VDDQ

2.5V

(DDR SDRAM)

AVDD

MVAVDD

SVAVDD

MAVDD

DAVDD

AAVDD

VDD33

VDD12

2.5V

XWAIT

XIREQ

MMA13

MMA0

XCD2

1.2V

3.3V

PEAKS_Lite(2/3)

HDSL PEAKS_Lite

IC8013

OP AMP

IC8031

3

2

7

1

5

6

SUB 9V

256M DDR_SDRAM

IC8009

64M CPU FLASH ROM

IC8019

MMDQ0

MMDQ31

XECSO-XECS5

10

TU8001

IF_AGC

ANT_V_SUPPLY

7

V_SUPPLY

11

5

SDA

1

IFD1

DVB TUNER

4

SCL

9

PEAKS_Lite(3/3)

PEAKS_Lite(1/3)

DATA BUS

ADDRESS BUS

CONTROL BUS

DATA BUS

ADDRESS BUS

CONTROL BUS

XRST

ENABLE0

CHPSYNC0

SCHDATA0

SCHCLK0

45

INTERFACE)

19

58

51

46

37

CI SLOT

63

20

62

8

36

67

44

59

57

JK8401

18

42

17

15

7

16

(COMMON

66

41

52

9

CONTROL BUFFER

IC8404

DATA BUFFER

IC8402

IC8213

BUFFER

IC8412

BUFFER

BUFFER

IC8410,IC8411

64

Vpp1,Vpp2

VCC

RESET

A0~A14

CE1#,CE2#

OE#,WE#

IORD#,IOWR#

IREQ#

CD1#,CD2#

MCLK0,WAIT#

MOVAL,MOSTRT

MDO3~MDO7

MDO0~MDO2

MISTRT

MDI0~MDI7

MIBAL,MCLKI

IFD2

XV

D-TV INTERFACE

DG0-DQ15

A0-A21

WP,WE,CE,OE

RESET

OUT

6

8

OUT

2

FLG

7

IN

EN

1

CARD 5V

IC8401

SUB 5V

XIRQ2

SCLT

18

SDAT

19

XTALI

62

XTALO

63

IMM

9

IMP

10

RESET

12

42

LOCK/OP2

SCL 20

SDA 21

D0 34

D3 31

STROUT 23

D4 29

CLKOUT 36

D/XP 38

25

D7

IC8003

COFDM DEMODULATOR

AGC1

16

IC8408

TS BUFFER

IC8409

TS BUFFER

SCL1

SDA1

3.3V(1.1A)

IC8024

SW

1.2V(0.8A)

VIN

SUB 9V

4

INV

3

2

FB

DC-DC CONV.1.2V

1

8

PVIN

DATA

VOUT

AVR +1.8V

3.3V

IC8864

1

7

+1.8V

VIN

3.3V

BOOTSWAP,XEDK

ELLK,XEWE2,XEWE3

XIORD,XIOWR

XWE,XOE,REG

XECS3

ED31

ED16

EA24

EA0

XCD1

XECSO,XERE

XEWE2,PWP

HSCLKIN

HSSYNCIN

HSVALIN

HSDIN7

HSDIN0

EVTRG

DATA

ADDRESS

CONTROL

CONTROL

DATA

24.167MHz

RESET

CI I/F

SUPPORT CARD&

NOR FLASH ROM

I/F

XCD1,XCD2,XWAIT,XIREQ

CHCLK,CHVAL,CHSYNC

EA1-EA15

72

CVBS

AF_VDACOUT5

D0~D7

6

2

30

32

14

29

10

21

50

56

47

53

Q8101

CVBS

XDACRST

AOUTR 10

IC8029

AUDIO DAC

11

AOUTL

SUB 5V

14

SPDATA0~7

SPEN,SPCLK

STROUT

DDR-

SDRAM

DACCK

DMIX

1

5

PDN

LRCK

MCLK

4

LRCK

SDTI

SRCK

BICK

3

2

3.3V

SUB 5V

XIRQ1

XIRQ2

VC27

CK27

INTERRUPTION

1

2

3

4

5

6

VCXO27M

IC8501

CIRESET

CIPOWER

ED16-ED23

XIRQ1

XERE,ERXW

XFERSTO

97

REG#

61

XRST

TH-37/42PE55E

XV-Board Block Diagram

TH-37/42PE55E

XV-Board Block Diagram

87

Summary of Contents for TH-42PE55E

Page 22: ...22 PDF created with pdfFactory Pro trial version www pdffactory com ...

Page 29: ...9 3 Option Description 29 PDF created with pdfFactory Pro trial version www pdffactory com ...

Page 30: ...30 PDF created with pdfFactory Pro trial version www pdffactory com ...

Page 49: ...49 PDF created with pdfFactory Pro trial version www pdffactory com ...

Page 51: ...51 PDF created with pdfFactory Pro trial version www pdffactory com ...

Page 129: ...14 Block and Schematic Diagram 14 1 Schematic Diagram Notes 67 ...

Page 130: ...14 Block and Schematic Diagram 14 1 Schematic Diagram Notes 67 ...