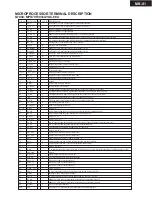

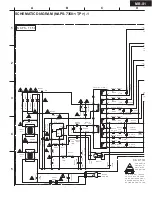

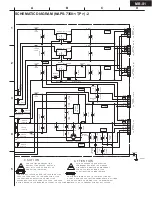

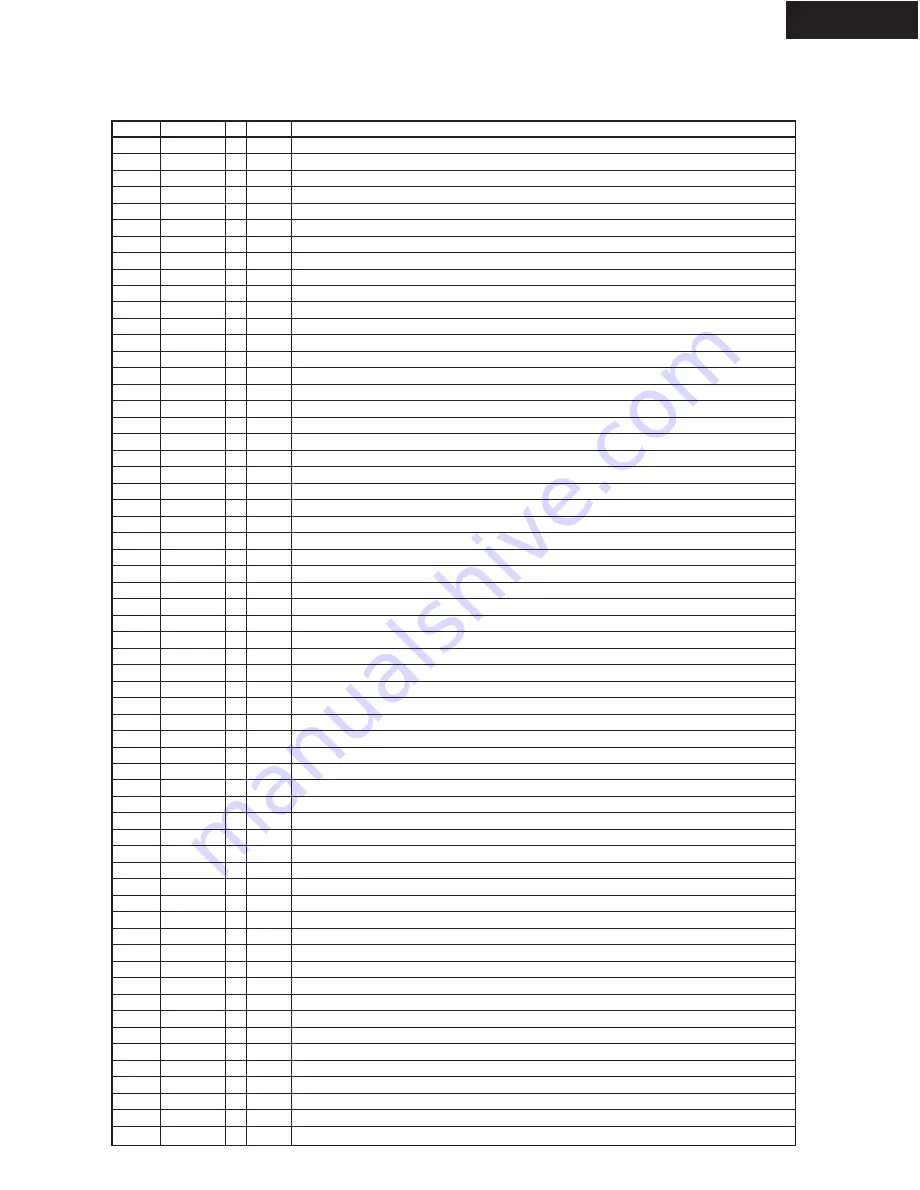

MB-S1

MICROPROCESSOR TERMINAL DESCRIPTION

Q7004: MPD70F3033AYGC-8EU

PIN NO. FUNCTION I/O LOGIC DESCRIPTION

1

SO2

O

uPD780232(FL TUBE) Synchronous serial output terminal

2

~SCK2

I/O

uPD780232(FL TUBE) Synchronous serial CLK terminal

3

RXD1

I

RS-232C(PHAST) input terminal

4

TXD1

O

RS-232C(PHAST) output terminal

5

~WP/ACC

O

MBM29DL (flash ROM) write-protection / acceleration terminal

6

EVDD

-

An input-and-output port and positive power supply supply for combination functional terminals

7

EVSS

-

An input-and-output port and grand potential for combination functional terminals

8

RY/~BY

I

A MBM29DL (flash ROM) ready / busy terminal

9

MUTE

O

H

Muting ON/OFF terminal

10

SUBMRST

O

L

MB89580 (USB microcomputer) reset terminal (Up (S))

11

FLMRST

O

L

uPD780232 (FL microcomputer) reset terminal (Up (S))

12

USBHRST

O

L

uPD72012 (USB hub tip) reset terminal (Up (S))

13

USBD+

O

H

USB D+ control terminal (being high pull-up)

14-16

A13-A15

O

Address bus 13-15

17

CIRON/OFF O

H

Circuit power supply ON/OFF

18

IC/VPP

-

Internal connection (it connects with VSS)

19-30

A1-A12

O

Address bus 5-12, 1-4

31

~RESET

I

System reset input

"32,33"

"XT1,XT2"

I

Oscillation connection for sub clocks

34

REGC

-

Regulator output stable capacity connection

"35,36"

"X2,X1"

I

Oscillation connection for main clocks

37

VSS

-

Ground

38

VDD

-

Positive power supply terminal

39

CLKOUT

O

Internal system clock output

40

~WRL

O

L

The low rank data light strobe signal terminal of the 16 bit data bus of external

41

~UBEN

O

L

The higher rank byte enable signal output terminal of the 16 bit data bus of external

42

~WRH

O

L

The higher rank data light strobe signal terminal of the 16 bit data bus of external

43

~RD

O

L

The lead strobe signal terminal of the 16 bit data bus of external

44

ASTB

O

The latch strobe signal output terminal of an external address bus

45

CDLED

O

H

CD LED/Program WR Start

46

HDDLED

O

H

HDD LED/Program WR Start

47-54

D0-D7

I/O

Data bus 0-7

55

BVDD

-

A bus interface and the positive power supply terminal for combination ports

56

BVSS

-

A bus interface and the grand terminal for combination ports

57-64

D8-D15

I/O

Data bus 8-15

65-70

A16-A21

I/O

Address bus 16-21

71

AVDD

-

A A/D converter and the analog positive power supply supply terminal for combination ports

72

AVSS

-

A A/D converter and the grand terminal for combination ports

73

AVREF

-

The standard voltage supply terminal for A/D converters

74

(intact) (Up (H))

75

PRVSW1

I

Destination distinction switch 1 (temporary)

76

PRVSW2

I

Destination distinction switch 2 (temporary)

77

SW1

I

Model distinction switch (L:MB-S1 H:HDR -1)

78

SW2

I

L

General-purpose switch 2 (main program forcible download switch)

79

SW3

I

L

General-purpose switch 3 (for an external ROM/RAM check)

80-85

(intact) (Up (H))

86

NMI

I

"The terminal for power failure detection (it will input, by the time it will fall completely, if voltage begins to fall) "

87

FROMA0

O

(intact)

88

D_MUTE

O

Digital output muting terminal (Up (H))

89

FLRDY

I

H

FL microcomputer data ready input terminal

90

ELVOL1

Electronic volume control terminal 1

91

ELVOL2

Electronic volume control terminal 2

92

ELVOL3

Electronic volume control terminal 3

93

GAIN_CTL

O

GAIN CTL port

94

SDA0

I2 C-bus terminal for QPICT board connection (DATA LINE) (Up (H))

95

QPINT

O

L

Interrupt QPICT board signal terminal

96

SCL0

I2 C-bus terminal for QPICT board connection (CLK LINE) (Up (H))

97

RXD0

MB89580 (USB sub microcomputer) asynchronous serial input terminal

98

TXD0

MB89580 (USB sub microcomputer) asynchronous serial output terminal

99

QPRST

O

L

QPICT reset signal terminal

100

SI2

uPD780232 (FL microcomputer) synchronous serial input terminal

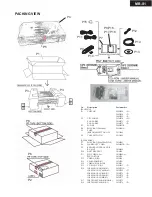

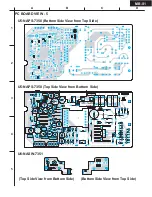

Summary of Contents for MB-S1

Page 27: ......