5- 24

M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL

MOTOROLA

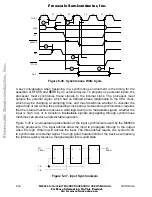

The MC68010 also differs from the other microprocessors described in this manual

regarding bus errors. The MC68010 can detect a late bus error signal asserted within one

clock cycle after the assertion of data transfer acknowledge. When receiving a bus error

signal, the processor can either initiate a bus error exception sequence or try running the

cycle again.

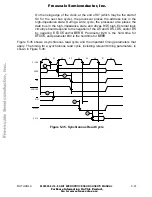

5.4.1 Bus Error Operation

In all the microprocessors described in this manual, a bus error is recognized when

DTACK

and

HALT

are negated and

BERR

is asserted. In the MC68010, a late bus error is

also recognized when

HALT

is negated, and

DTACK

and

BERR

are asserted within one

clock cycle.

When the bus error condition is recognized, the current bus cycle is terminated in S9 for a

read cycle, a write cycle, or the read portion of a read-modify-write cycle. For the write

portion of a read-modify-write cycle, the current bus cycle is terminated in S21. As long as

BERR

remains asserted, the data and address buses are in the high-impedance state.

Figure 5-25 shows the timing for the normal bus error, and Figure 5-26 shows the timing

for the MC68010 late bus error.

S0

S2

S4

S6

CLK

FC2–FC0

A23–A1

w

w

w

w

S8

AS

LDS/UDS

R/W

DTACK

D15–D0

BERR

HALT

INITIATE

BUS ERROR

DETECTION

INITIATE BUS

ERROR STACKING

RESPONSE

FAILURE

READ

Figure 5-25. Bus Error Timing Diagram

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..