5- 22

M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL

MOTOROLA

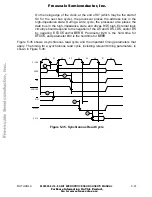

S0 S1 S2 S3 S4 S5 S6 S7

S0 S1 S2 S3 S4

CLK

BR NEGATED

BG ASSERTED AND BUS THREE STATED

BR VALID INTERNAL

BR SAMPLED

BR ASSERTED

BR

BG

BGACK

FC2–FC0

A23–A1

AS

UDS

LDS

R/W

DTACK

D15–D0

BUS RELEASED FROM THREE STATE AND PROCESSOR STARTS NEXT BUS CYCLE

PROCESSOR

PROCESSOR

BUS

INACTIVE

ALTERNATE BUS MASTER

Figure 5-23. 2-Wire Bus Arbitration Timing Diagram—Bus Inactive

F

re

e

sc

a

le

S

e

m

ic

o

n

d

u

c

to

r,

I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

n

c

.

..