Inter-Integrated Circuit Peripherals

UG0331 User Guide Revision 15.0

541

15.2.3

Initialization

The I

2

C peripheral can be initialized in the user application software by configuring the I

2

C Control

register and SOFT_RESET_CR system registry. The initialization sequence is as follows:

1.

Release the I

2

C from reset by using SOFT_RESET_CR system registry (

page 540).

2.

Enable I

2

C by writing ‘1’ to the ENS1 bit of

3.

Configure the serial clock rate by using CR0, CR1, and CR2 bits of

4.

Set the slave address to Slave0 Address Register (

).

15.2.3.1 I

2

C Reset

The I

2

C peripherals reset to zero on power-up and are held in reset until enabled. An option is provided

under software control to reset the I

2

C peripherals by writing to bit 11 or bit 12 in the System register,

SOFT_RESET_CR. The soft resets are encoded in the following table.

At power-up, the reset signals are asserted as 1. This keeps the I

2

C peripherals in a reset state. I

2

C

peripheral becomes active when the bit is set to 0, as shown in

15.2.3.2 I

2

C Clock Requirements

The I2C_0 and I2C_1 peripherals are clocked by APB_0_CLK on APB bus 0 and APB_1_CLK on APB

bus 1. These clocks are derived from the main MSS clock M3_CLK. Each APB clock can be

programmed individually as M3_CLK divided by 1, 2, 4 or 8. Refer to the

IGLOO2 Clocking Resources User Guide

for more information.

15.2.3.2.1 Baud Rate Clock

BCLK is a pulse-for-transmission speed control signal and is internally synchronized with the clock input.

BCLK is used to set the serial clock frequency from a clock sourced within the FPGA fabric when the

CR[2:0] bits in the Control register are set to 0b111(0x7). Otherwise, either APB_0_CLK or APB_1_CLK

is used to determine the serial clock frequency. The actual non-stretched serial bus clock frequency can

be calculated based on the settings in the CR[2:0] fields of the Control register and the frequencies of

APB_0_CLK or APB_1_CLK and BCLK. Refer to the

page 551 for more information on

bit settings.

15.2.3.2.2 Clock Stretching

The I

2

C peripherals support the clock stretching feature as defined in Philips I

2

C v2.1 specifications. This

addresses the condition where the I

2

C slave is unable to meet the clock speed provided by the I

2

C

master and needs to slow down. Care should be taken so that the slowest I

2

C device does not dominate

the bus performance. The I

2

C slave is allowed to hold down the clock if it needs to reduce the bus speed.

The I

2

C master reads back the clock signal after releasing it to a High state and waits until the line goes

High.

Clock stretching is a common practice. However, the total bandwidth of the shared bus might significantly

decrease. Estimating the impact of clock stretching is required to share I

2

C bus among multiple devices.

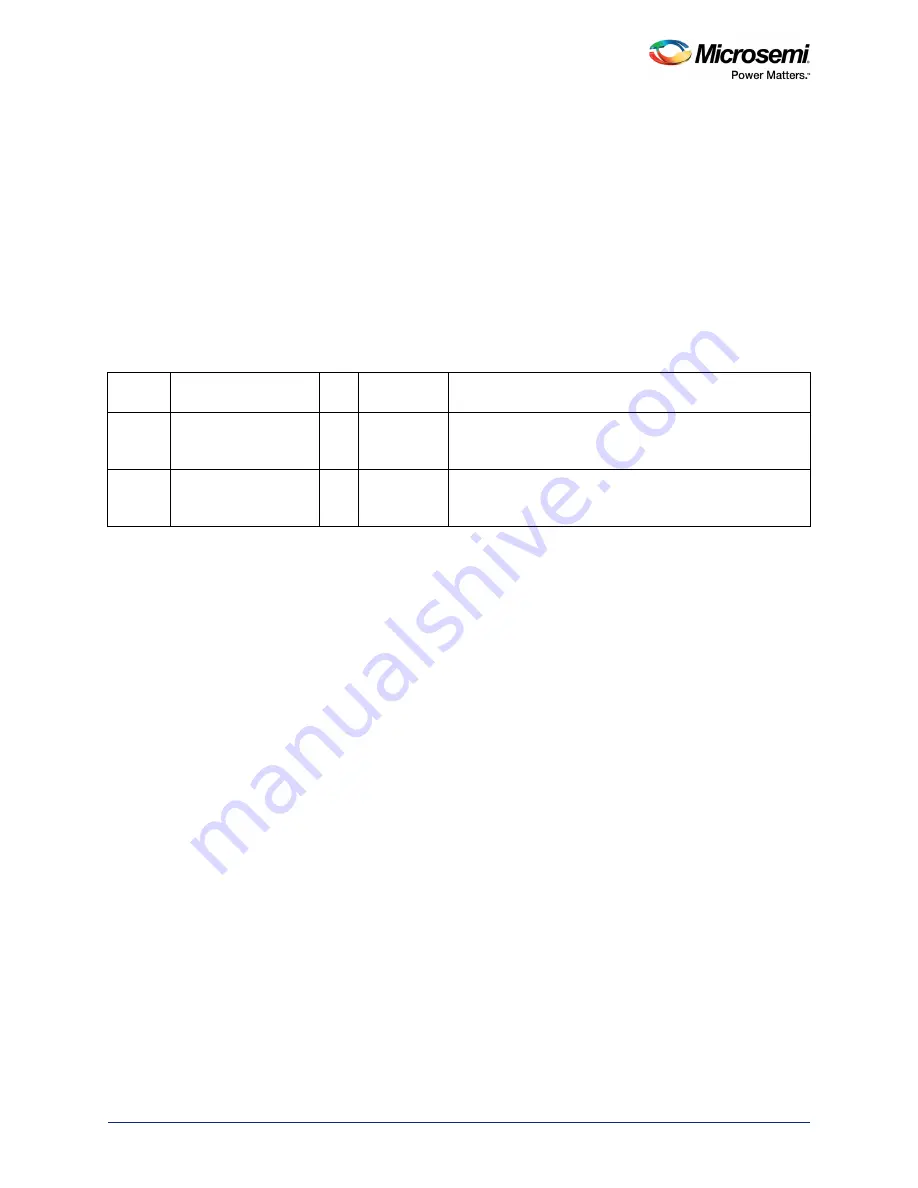

Table 518 •

Soft Reset Bit Definitions For I

2

C Peripherals

Bit

Number Name

R/W Reset Value Description

12

I2C1_SOFTRESETR

R/W 1

Controls reset input to I2C_1

0: Release I2C_1 from reset

1: Keep I2C_1 in reset (reset value)

11

I2C0_SOFTRESET

R/W 1

Controls reset input to I2C_0

0: Release I2C_0 from reset

1: Keep I2C_0 in reset (reset value)