Serial Peripheral Interface Controller

UG0331 User Guide Revision 15.0

530

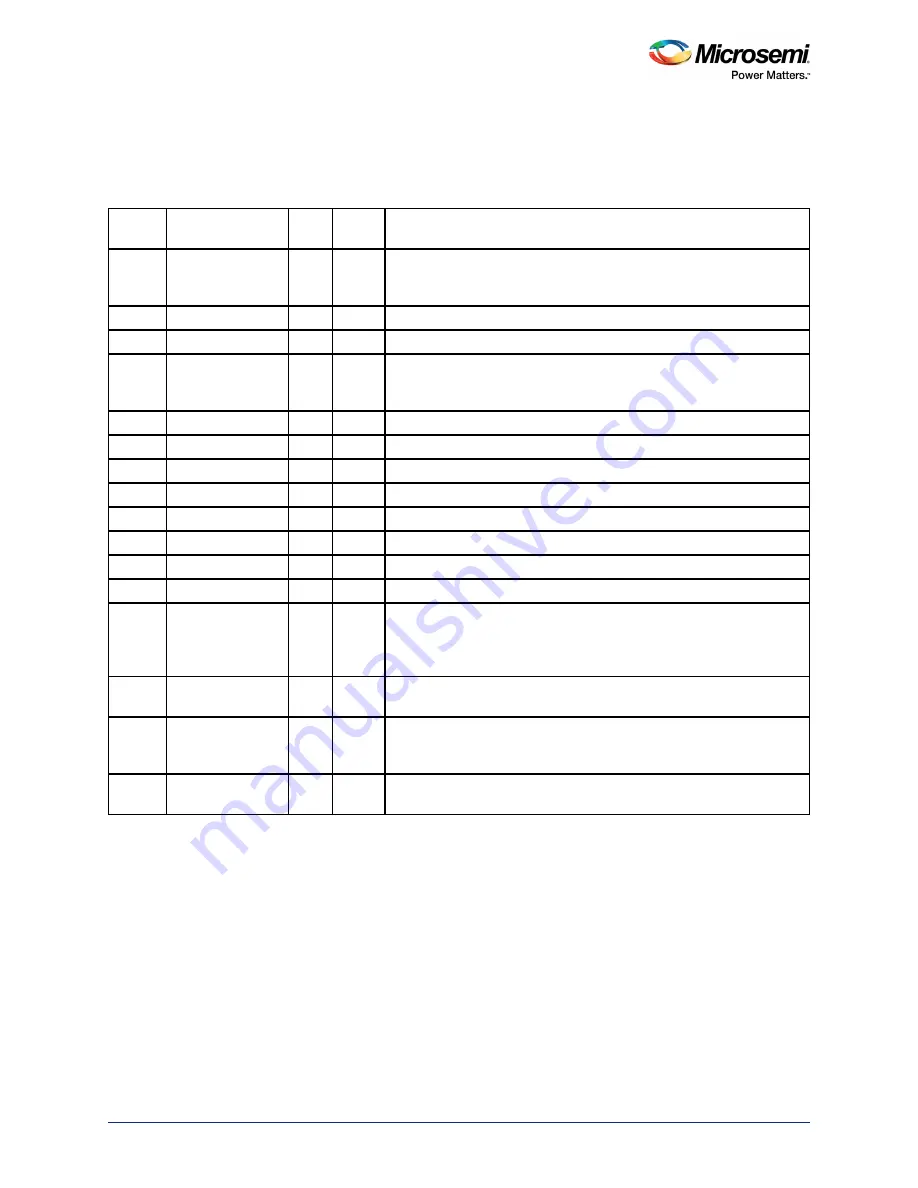

14.4.3.3 SPI Status Register (STATUS)

The following table provides the SPI Status register details. This register indicates the state of SPI such

as Tx/Rx FIFO, Tx under-run, and Rx overflow.

Notes:

•

Bits [11:4] correspond to FIFO status.

•

None of these status bits are sticky. During run-time, the status of these bits reflects the current

status of SPI.

•

To determine the cause of an interrupt, the masked interrupt status (MIS) register must be read.

Table 502 •

Status

Bit

Number Name

R/W

Reset

Value

Description

[31:15]

Reserved

R/W

0

Software should not rely on the value of a reserved bit. To provide

compatibility with future products, the value of a reserved bit should be

preserved across a read-modify-write operation.

14

ACTIVE

R

SPI is still transmitting or receiving data.

13

SSEL

R

Current state of SPI_X_SS[0]

12

FRAMESTART

0: SPI output enable is active as required.

1: SPI output enable is not asserted. Allows multiple slaves to share a

single slave select signal with a single master.

11

TXFIFOEMPNXT

R

0

Transmit FIFO empty on next read

10

TXFIFOEMP

R

1

Transmit FIFO is empty

9

TXFIFOFULNXT

R

0

Transmit FIFO full on next write

8

TXFIFOFUL

R

0

Transmit FIFO is full

7

RXFIFOEMPNXT

R

0

Receive FIFO empty on next read

6

RXFIFOEMP

R

1

Receive FIFO empty

5

RXFIFOFULNXT

R

0

Receive FIFO full on next write

4

RXFIFOFUL

R

0

Receive FIFO is full

3

TXUNDERRUN

RO

0

No data available for transmission. The channel cannot read data from

the transmit FIFO because the transmit FIFO is empty. Certainly this

can only be raised in slave mode because the master will not attempt

to transmit unless there is data in FIFO.

2

RXOVERFLOW

RO

0

Channel is unable to write to receive FIFO as it is full. Applies to

master and slave modes.

1

RXDATRCED

RO

0

When set, it indicates that the number of frames specified by

TXRXDFCOUNT has been received and can be read. Applies to

master and slave modes.

0

TXDATSENT

RO

0

When set, it indicates that the numbers of frames specified by

TXRXDFCOUNT has been sent. Applies to master and slave modes.