3. TECHNICAL BRIEF

- 4 -

Copyright © 01 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

3.4 Crystal(26 MHz, X100)

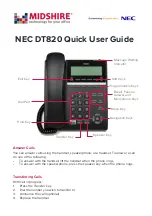

Figure. 3.4.1 Clock distributions inside the MT6251.

These blocks with shadow are analog circuits.

Copyright © 2012 LG Electronics. Inc. All right reserved.

O nly for training and service purposes

LGE Internal Use Only

21

3.4 Crystal(26 MHz, X100)

3. TECHNICAL BRIEF

Figure. 3.4.1 Clock distributions inside the MT6251.

These blocks with shadow are analog circuits.

There are two major time bases in the MT6251. For the faster one is the 26MHz clock originating from the digital

control oscillator(DCXO) of RF chip. This signal is then converted to the square-

XBWF TJHOBM UISPVHI $-,425IF

other time base is the 32.768 KHz clock generated by an on-chip oscillator connected to an external crystal .

Figure 3.4.1 shows the clock sources as well as their utilizations inside the chip.

(64mhz)

(64mhz)

UPLL_64M_CK

UPLL_48M_USB_CK

MPLL_CK

CLKSQ_6M_CK

FUSB_48M_CK

FUSB_78M_CK

FGSM_5M_CK

TEST_CK

TEST_CK

TEST_CK

HDSP_104M_CK

HSF_78M_CK

HBUS_78M_CK

TEST_CK

TEST_CK

HMCU_78M_CK

HMCU_78M_CK

HBUS_78M_CK

HSF_78M_CK

HDSP1_104M_CK

HDSP_104M_CK

FGSM_5M_CK

FUSB_78M_CK

TEST_CK

FUSB_48M_CK

upllsel

upllsel

upllsel

mpllsel

mpllsel

mpllsel

hbus_divcks

sfpllsel

hsf_divcks

hdsp_divcks

dspllsel

FHCTL_MPLLSEL

(frequency hopping switch)

104M

5M

78M

48M

104M

104M

78M

78M

CLKSW_TOP

GSMRF

ABB

6MHz

DCXO

MPLL

UPLL

UPLLDIV

MPLLDIV

USB PHY

HMCUCNT

HSFCNT

EN

EN

GG

EN

GG

EN

GG

EN

GG

HDSP1_EN

HDSP_EN

HDSP_DCM

HDSP1_DCM

HSF_DCM

HBUS_DCM

divcks

divcks

divcks

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

-i

-i

-i

-i

-i

-i

-i

-i

-i

-i

-i

-i