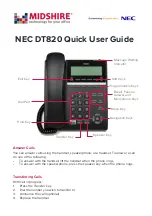

7. CIRCUIT DIAGRAM

- 110 -

LGE Internal Use Only

Copyright © 2009 LG Electronics. Inc. All right reserved.

Only for training and service purposes

QSC6240_DATA,QSC6240_POWER

U201

2

2

V

9

1

C

A

6

1

B

A

2

2

C

A

1

1

B

A

2

1

T

4

1

R

3

2

C

A

2

2

B

1

2

B

0

2

B

3

2

A

6

1

J

5

1

J

6

1

H

5

1

H

W14

Y22

U22

W15

AA22

AB12

W13

W12

V21

W21

AB13

AA13

AC11

AC12

AB14

AA14

AC20

AB19

AB7

AB18

W16

AA18

AC18

R19

AB17

AC17

M18

AB15

AC15

R23

T18

AA19

N18

AA15

C20

AA12

H18

U21

AC21

C18

AC16

D21

AA20

C19

AA16

E18

AA17

D23

AC14

D22

V16

H19

T13

K18

J19

U2

G19

U1

K21

L13

G21

L12

K19

L11

L10

B18

K13

K12

A18

K11

K10

C23

C3

B2

B23

A1

A22

A15

A19

A20

R3

A21

N3

L3

L22

J3

K22

G3

L23

A9

K23

A6

J23

A12

H23

V13

J22

H22

V14

V15

G23

F23

1

2

B

A

0

2

B

A

9

1

U

8

1

W

8

1

U

7

1

V

7

1

W

0

1

V

9

V

3

2

U

3

2

V

2

2

T

3

1

C

A

3

2

Y

2

2

W

3

2

W

9

B

A

0

1

C

A

9

C

A

1

1

A

A

0

1

A

A

2

1

V

1

1

V

3

2

B

A

3

2

A

A

8

1

V

0

1

W

1

1

W

1

2

Y

2

2

B

A

1

2

A

A

9

1

V

9

1

W

0

_

N

O

_

A

P

_

G

1

_

N

O

_

A

P

_

G

0

_

N

O

_

A

P

_

U

1

_

N

O

_

A

P

_

U

2

_

N

O

_

A

P

_

U

1

P

G

_

N

E

_

O

X

1

P

G

_

T

U

O

_

O

X

2

P

G

_

T

U

O

_

O

X

NI

_

K

2

3

_

L

A

T

X

T

U

O

_

K

2

3

_

L

A

T

X

D

L

O

H

_

S

P

K

L

C

_

P

E

E

L

S

N

_

R

W

P

_

D

P

K

L

T

C

_

A

P

_

T

U

O

V

P

Y

B

_

F

E

R

4

P

P

M

P

C

N

_

D

N

G

F

E

R

_

C

D

A

_

O

X

NI

_

C

D

A

_

O

X

C

D

A

_

O

X

_

D

N

G

M

R

E

H

T

_

F

E

R

V

0

NI

A

K

H

NI

_

M

9

1

_

L

A

T

X

T

U

O

_

M

9

1

_

L

A

T

X

O

X

_

D

2

D

N

_

T

E

S

E

R

_

N

O

P

N

_

V

R

D

_

D

C

L

3

P

P

M

_

N

_

V

R

D

_

D

P

K

N

_

V

R

D

_

BI

V

2

P

P

M

S

AI

B

_

D

E

S

H

P

_

T

U

O

_

R

K

P

S

M

_

T

U

O

_

R

K

P

S

RX_IN_G_HBM

RX_IN_G_HBP

VREG_USB_2P6

VREG_USB_3P3

RX_IN_G_LBM

RX_IN_G_LBP

VDD_EFUSE

RX_IN_U_G_HB1M

VDD_P5

RX_IN_U_G_HB1P

VDD_P2_1

RX_IN_U_HB2M

VDD_P2_2

RX_IN_U_HB2P

VDD_P1_1

RX_IN_U_G_LBM

VDD_P1_2

RX_IN_U_G_LBP

VDD_P1_3

VDD_P1_4

TX_OUT_U_HB1

VDD_P1_5

TX_OUT_U_HB2

TX_OUT_U_LB

VDD_P6

TX_OUT_G_HB

VDD_CORE1

TX_OUT_G_LB

VDD_CORE2

VDD_CORE3

PWR_DET_IN

VDD_CORE4

VDD_CORE5

PA_DAC

VDD_CORE6

VDD_CORE7

TX_DAC_REF_BYP

VDD_CORE8

VDD_CORE9

VDD_RFRX1

VDD_CORE10

VDD_RFRX2

VDD_CORE11

VDD_RFRX3

VDD_CORE12

VDD_RFRX4

VDD_CORE13

VDD_RFRX5

VDD_RFRX6

VREG_MPLL

VDD_RFRX7

VDD_USB

VDD_RFTX1

VDD_RF1

VDD_RFTX2

VDD_RX2_TX2

VDD_RFTX3

VDD_PLL_CDC

VDD_RFTX4

VDD_NCP

VDD_RFTX5

VDD_RF2

VDD_RFTX6

VDD_SPKR

VDD_TCXO

VDD_RFA1

VDD_PAD_SIM

VDD_RFA2

VDD_EBI_RFA

VDD_RFA3

VDD_MSMC

VDD_RFA4

VDD_RFA5

VSW_RF1

VREG_RF1

VREG_CDC2

VSW_RF2

VREG_RF2

HPH_VNEG

VSW_MSMC

VCOIN

VREG_RFA

NCP_CTC1

USB_VBUS

NCP_CTC2

VREG_NCP

VCHG1

VCHG2

VSW_5V

VREG_5V

VPH_PWR1

VPH_PWR2

VREG_RFRX2

VREG_RFTX2

BAT_FET_N

VREG_MSMP

VBAT

VREG_GP1

VREG_MSME

VREG_TCXO

VREG_GP2

VREG_USIM

1

C

N

D

2

C

N

D

3

C

N

D

4

C

N

D

0

0

1

_

F

R

_

A

_

D

N

G

1

0

1

_

F

R

_

A

_

D

N

G

2

0

1

_

F

R

_

A

_

D

N

G

3

0

1

_

F

R

_

A

_

D

N

G

5

C

N

D

GI

D

_

D

N

G

L

L

P

M

_

D

N

G

1

F

R

_

D

N

G

R

K

P

S

_

D

N

G

2

F

R

_

D

N

G

C

M

S

M

_

D

N

G

O

X

C

T

_

D

N

G

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

L

K

J

I

H

G

F

E

D

C

B

A

L

K

J

I

H

G

F

E

D

C

B

A

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

p

7

2

20

2

C

1

R201

+VPWR

0

R203

VREG_GP1_1.5V

K

7

42

0

2

R

10u

C203

4

0

2

C

u

2.

2

VREG_MICROSD_3.0V

2.2u

C205

33u

C206

VREG_RF1_2.3V

7

0

2

C

n

0

0

1

u

7.

48

0

2

C

u

7.

49

0

2

C

C210

4.7u

HOLE

OJ201

n

0

0

11

1

2

C

VREG_RFTX2_1.3V

15n

L201

p

0

0

12

1

2

C

3

1

2

C

u

7.

4

VREG_RFTX2_1.3V

u

2.

24

1

2

C

u

7.

45

1

2

C

VREG_MSMC_1.2V

u

7.

46

1

2

C

C217

10u

+VPWR

27n

L202

8

1

2

C

u

7.

4

9

1

2

C

n

0

0

1

100n

C220

1

2

2

C

n

0

0

1

VREG_TCXO_2.85V

SIA411DJ

Q201

S1

S2

G

D1

D2

D3

D4

D5

2

2

2

C

n

0

1

n

0

0

13

2

2

C

L203

4.7u

4

2

2

C

u

7.

4

DNI

C225

6

2

2

C

p

0

0

1

4.7u

L204

u

17

2

2

C

VBUS

8

2

2

C

n

0

0

1

+VPWR

VREG_RFRX2_1.3V

VREG_MSMP_2.6V

u

2.

29

2

2

C

VREG_USIM_2.85V

C230

100n

1

3

2

C

n

0

0

1

n

0

0

12

3

2

C

VREG_MSME_1.8V

3

3

2

C

u

0

1

VREG_MSME_1.8V

n

0

0

14

3

2

C

DNI

C235

n

0

0

16

3

2

C

7

3

2

C

n

0

0

1

8

3

2

C

n

0

0

1

u

19

3

2

C

VREG_RF2_1.4V

VREG_RFRX2_1.3V

100n

C240

p

0

0

12

4

2

C

3

4

2

C

u

2.

2

4

4

2

C

n

0

0

1

L205

5

4

2

C

n

0

0

1

VREG_MSMP_2.6V

HOLE

OJ203

6

4

2

C

n

0

0

1

7

4

2

C

p

0

0

1

8

4

2

C

n

0

0

1

9

4

2

C

u

1

p

0

0

1

05

2

C

1

5

2

C

u

0

1

2

5

2

C

u

2.

2

3

5

2

C

u

0

1

4

5

2

C

n

0

0

1

4.7u

C255

L206

4.7u

u

2.

26

5

2

C

VREG_MSMC_1.2V

7

5

2

C

p

0

7

2

n

0

0

18

5

2

C

VREG_RFA_2.2V

27n

L207

OJ205

HOLE

C259

10u

VREG_RF1_2.3V

VREG_RFA_2.2V

FC-255

X201

32.768KHz

VREG_RF2_1.4V

1u

C260

1

6

2

C

n

0

0

1

HOLE

OJ206

2

6

2

C

u

2.

2

R205

0

K

L

C

_

P

E

E

L

S

_

D

2

D

WLNA_HB2_IN_M

WLNA_HB2_IN_P

WLNA_LB_IN_P

WLNA_LB_IN_M

WCDMA_2100_TX_OUT

WCDMA_900_TX_OUT

WLNA_HB1_IN_M

WLNA_HB1_IN_P

GLNA_HB_IN_M

GLNA_HB_IN_P

GLNA_LB_IN_M

GLNA_LB_IN_P

GSM_PA_RAMP

D

N

A

B

_

A

P

_

M

S

G

N

E

_

A

P

_

M

S

G

TX_GSM_LB

TX_GSM_HB

NI

_

L

A

T

X

_

M

9

1

1

N

O

_

A

P

_

A

M

D

C

W

PWR_DET

S

AI

B

CI

M

VBATT

VBATT

T

H

GI

L

K

C

A

B

_

D

B

Y

K

P

M

E

T

_

T

T

A

B

V

N

_

NI

S

E

R

_

M

S

M

T

H

GI

L

K

C

A

B

_

B

U

S

D

L

O

H

_

S

P

T

U

O

_

M

R

E

H

T

_

F

E

R

V

N

_

R

W

P

D

P

K

N

_

R

E

W

O

P

_

R

O

T

O

M

0

N

O

_

A

P

_

A

M

D

C

W

VBACK_UP

VREG_RF2

VREG_RF2_1.4V|VREG_RF2

VSW_MSMC

VSW_MSMC

VSW_RF2

VSW_RF2

VSW_RF1

VSW_RF1

BATT_FET_N

BATT_FET_N

VREG_RF1

VREG_RF1_2.3V|VREG_RF1

WCDMA_1900_TX_OUT

VDD_MSMC

F

R

_

A

_

D

N

G

Digital POWER

C

N

D

VDD_NCP

N

_

V

R

D

_

D

C

L

3

P

P

M

_

N

_

V

R

D

_

D

P

K

UNDER INVESTIGATION ABOUT CURRENT CONSUMPTION

SPEAKER GROUND

VDD_RF2

0

C

D

A

K

H

PMIC control

F

R

_

A

_

D

N

G

SMPS Circuit

F

R

_

A

_

D

N

G

PMIC POWER

F

R

_

A

_

D

N

G

4

P

P

M

VDD_RF1

TP for UART calibration

close to QSC