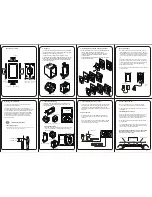

ATSC Half NIM

DIF

SIF

Parallel TS

System

Demux

Audio DSP

Multi-STD

Audio Decoder

BTSC AFE

w/ PLL

1ch L/R

Audio-ADC

24b@48KHz

GBB AFE

1ch@30MHz

w/ PLL

Global Baseband

V/Q, DVB-T/C

CVBS(6ch)

Component(2ch)

3ch Video

AFE

10b@165MHz

w/ LLPLL

HDMI-Rx 1.4

(1-port PHY)

3D, 4kx2k

HDMI(1ch)

Capture

Block

(3CH)

AAD

(THAT)

Audio Codec1

(Digital Part)

Mux

Analog Chip

Digital Chip

Audio L/R (5-ch)

SW

I2S(stero)

Sound

DSP

I2S

SPDIF

Video Decoder

(

Dual HD

)

CVBS AFE(2-ch)

12b@54MHz

12 : CVBS

Mux

12

Diplay

Engine

MC NR,

Vertical MC IPC

Scaler, PE

OSD, VCR

LVDS

H.264 Encoder

SD upto 480p

12

PHY

(3-port)

USB2.0

Host (x3)

DDR3-PHY

DDR3(x16) * 3

Ethernet

MAC

eMMC

Controller

CPU

Dual C-A9 (1GHz)

Graphic

Engine

2D-VG / 3D Open-ES2.0

Audio

10(data)+1(en)+5(gc)

4(val, err, clk, sop)

+8 (data)

I2C

I2C

6(gbb, l9da)

I2C

Digital

Audio

Output

LVDS

LVDS

Video

LVDS

Video

OSD

LVDS

Audio PLL

w/ DCO

I2S (mono)

3(lrck, lrch, sck)

I2C

SW

SW

3D or UD

Data bridge

I2S or SPDIF

8

Audio Clocks

9

1ch mono

Audio-ADC

24b@48KHz

Audio Codec0

(Digital Part)

Mux

LVDS

interrupt

3(hdmi, 3ch, gbb)

3(lrck, lrch, sck)

Audio

HDMI

(1-Link)

Tuner_CVBS

L9 Block diagram

Copyright ⓒ 2013 LG Electronics. Inc. All right reserved.

Only for training and service purposes

LGE Internal Use Only

Summary of Contents for 50GA6400

Page 49: ......