Kvaser PCIEcan User's Guide

10(17)

Kvaser AB, Mölndal, Sweden

— www.kvaser.com

6 Software Development Information

This section is intended for those who want to program the PCIEcan card directly. Normally,

you would choose to use the supporting device drivers available for the PCIEcan card. Refer

to the “CANLIB Software Development Kit” documentation for further information on these

device drivers from a programm

er’s point of view. Please note that this board is fully software

compatible with the Kvaser PCIEcan boards.

6.1 Additional Documentation

This document includes all information you need to use the circuits on the card. However, the

circuits themselves are not described here so information about these must be obtained from

the suppliers. See the list of references in chapter 9. General knowledge about the PCI

Express bus is also assumed.

6.2 The PCI Express bus controller

All PCIEcan boards use the same PCI controller, which is a Xilinx FPGA with PCI core. The

PCI controller is responsible for address decoding and interrupt steering.

The initialization of the PCI controller is outside the scope of this manual. Typically, it is

carried out by the operating system and/or the BIOS. There are a few registers you have to

set up in the driver; these are described below.

6.3 Address decoding

The PCI Express controller can decode up to 5 different address areas, three of which are

used by the PCIEcan.

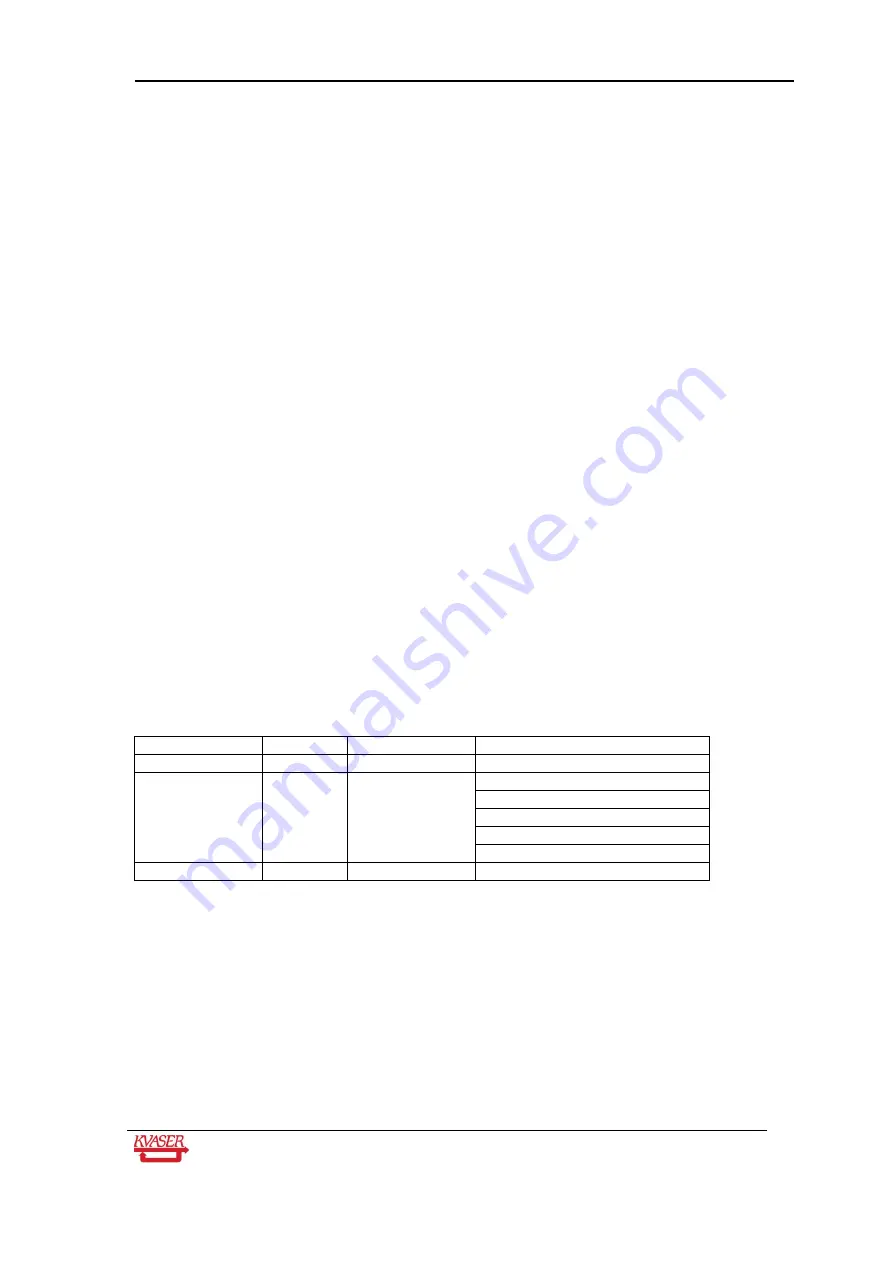

Address area #

Type

Size (bytes)

Used for

0

I/O

128

Xilinx registers

(“AMCC S5920”).

1

I/O

128

SJA1000 circuits

0

– 0x1f: SJA1000 #1

0x20

– 0x3F: SJA1000 #2

0x40

– 0x5F: SJA1000 #3

0x60

– 0x7F: SJA1000 #4

2

I/O

16

Xilinx registers

Address area number 1, the one used for the SJA1000’s, is further subdivided into four areas

of 32 bytes each; one for each (possible) SJA1000.

There is no actual AMCC S5920 in the PCIEcan, but the first address area is set up to be

compatible with the Kvaser PCIcan cards.