16

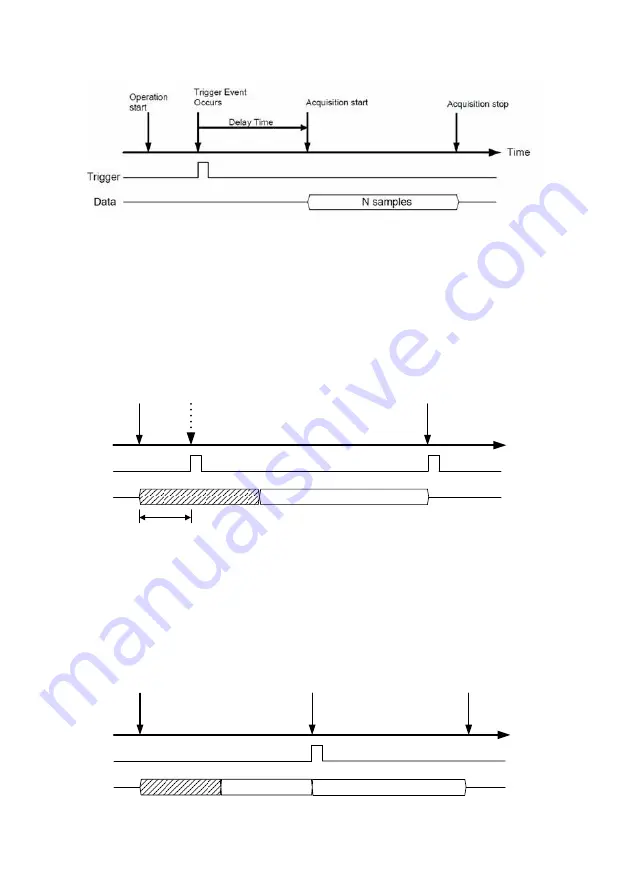

Figure 3-6: Delayed Trigger Mode Acquisition

3�4�3 Pre-Trigger Mode

Collects data before the trigger event, starting once specified function calls are executed to begin the

pre-trigger operation, and stopping when the trigger event occurs. If the trigger event occurs after

the specified amount of data has been acquired, the system stores only data preceding the trigger

event by a specified amount, as follows.

Time

Operation start

Acquisition start

Trigger

Data

Trigger Event Occurs

Acquisition stop

Data transfer to system begins

N samples

X samples have been acquired

before trigger occurs, where X<N

Trigger signals occuring before the specified

amount of data has been acquired are ignored

Figure 3-7: Pre-Trigger Mode Acquisition

3�4�4 Middle Trigger Mode

Collects data before and after the trigger event, with the amount to be collected set individually (M

and N samples), as follows

Time

Operation start

Acquisition start

Trigger

Data

Acquisition stop

Data transfer to system begins

N samples

M samples

Trigger event occurs

Figure 3-8: Middle Trigger Mode Acquisition