2-35

2-36

WF3

WF5

WF6

WF2

WF1

WF7

WF4

R

L

R

L

R

L

6

5

CN2001

CN2002

Q2051

Q2052-

Q2055

T2051

EQ

P

R

PRE

AMP

REC

ON

REC

VCA

DET

FIL

TER

FIL

TER

TRANS

OSC

PO

WER

SW

TO

SYSCON

3

0

+

-

2

1

A.MUTE

SP

ON

A.MUTE(H)

N.REC(H)

A.

ERASE

REC/PB

F.

ERASE

5

6

A/C

HEAD

2

1

N.REC_ST(H)

62

1

3

7

9

EP

( LP

)

ON

94

95

96

97

98

FULL

ERASE

HEAD

CN1

J2

REAR

OUT

+

3

1

NO

T

USED

2

1

IC2201

61

NORMAL

OUT

62

NORMAL

IN

2

53

LINE

OUT

( R

)

57

LINE

OUT

( L

)

FMA

CH1

A

UDIO HEAD

U

.DR

UM

CN1

FMA

CH2

J7101

8

6

J7101

7

5

3

4

9

EXT1

IN

( R

)

14

EXT1

IN

( L

)

22

CH1

21

COM

24

CH2

48

SIF

IN

36

MUTE

CTL

Q2201-

Q2204

MUTE

CONTR

OL

I2C

CLK

I2C

D

A

T

A

43

DA

TA

42

CLK

30

PB

FM

IN

H.REC_ST(H)

A

UDIO

( R

)

A

UDIO

( L

)

1

2

3

J1

REAR

IN

AU

D

IO

( R

)

AU

D

IO

( L

)

R

L

10

15

EXT2

IN

( R

)

EXT2

IN

( L

)

MAIN

( VIDEO/A

UDIO

,

FMA/DEMOD

, TERMINAL

)

FR

ONT

AU

D

IO

IN

( R

)

FR

ONT

AU

D

IO

IN

( L

)

PRE

OUT

29

7

8

9

3

4

4

3

TO

TUNER

SIF

IC1

(VIDEO/N.A

UDIO SIGNAL PR

OCESSOR)

PO

WER

SWITCH

PO

WER

AMP

FL

Y_REC_ST(H)

FL

Y_REC(H)

TRANS

OSC

PO

WER

SW

B2051

6

4

FULL_E.ON(H)

OPEN

59

RFC_OUT

RF_A

UDIO

27

AFF

28

ENV

A.ENV/ND(L)

A.FF

TP2253

A.PB_FM

SW

Q2062

Q2063

Q2061

T2052

10

11

FL

Y

.E

FL

YING ERASE

Q401

Q402

Q403-

Q405

Q2001-

Q2003

9

10

11

12

13

14

9

10

11

12

13

14

WF3

WF5

WF6

WF2

WF1

WF7

WF4

R

L

R

L

R

L

6

5

CN2002

Q2051

Q2052-

Q2055

T2051

EQ

P

R

PRE

AMP

REC

ON

REC

VCA

DET

FIL

TER

FIL

TER

TRANS

OSC

PO

WER

SW

TO

SYSCON

3

0

+

-

2

1

A.MUTE

SP

ON

A.MUTE(H)

N.REC(H)

A.

ERASE

REC/PB

F.

ERASE

5

6

A/C

HEAD

2

1

N.REC_ST(H)

62

1

3

7

9

EP

( LP

)

ON

94

95

96

97

98

FULL

ERASE

HEAD

CN1

J2

REAR

OUT

+

NO

T

USED

2

1

IC2201

61

NORMAL

OUT

62

NORMAL

IN

2

53

LINE

OUT

( R

)

57

LINE

OUT

( L

)

FMA

CH1

A

UDIO HEAD

U

.DR

UM

CN1

FMA

CH2

J7101

8

6

J7101

7

5

3

4

9

NC

NC

NO

T USED

14

EXT1

IN

( L

)

22

CH1

21

COM

24

CH2

48

SIF

IN

36

MUTE

CTL

Q2201-

Q2204

MUTE

CONTR

OL

I2C

CLK

I2C

D

A

T

A

43

DA

TA

42

CLK

30

PB

FM

IN

H.REC_ST(H)

A

UDIO

( R

)

A

R

L

10

15

2

4

EXT2

IN

( R

)

EXT2

IN

( L

)

MAIN

( VIDEO/A

UDIO

,

FMA/DEMOD

, TERMINAL

)

FR

ONT

AU

D

IO

IN

( R

)

FR

ONT

AU

D

IO

IN

( L

)

PRE

OUT

29

7

8

9

4

3

TO

TUNER

SIF

IC1

(VIDEO/N.A

UDIO SIGNAL PR

OCESSOR)

PO

WER

SWITCH

PO

WER

AMP

FL

Y_REC_ST(H)

FL

Y_REC(H)

TRANS

OSC

PO

WER

SW

B2051

6

4

FULL_E.ON(H)

59

RFC_OUT

RF_A

UDIO

27

AFF

28

ENV

A.ENV/ND(L)

A.FF

TP2253

A.PB_FM

SW

Q2062

Q2063

Q2061

T2052

10

11

FL

Y

.E

FL

YING ERASE

Q401

Q402

Q403-

Q405

Q2001-

Q2003

9

10

11

12

13

14

9

10

11

12

13

14

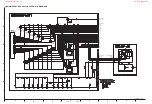

Note:F

or the w

a

v

ef

or

ms in this schematic diag

ram,ref

er to page 2-30.

AUDIO BLOCK DIAGRAM

+5V

+5V

( 14.32MHz

)

CTL

+

CTL

-

MAIN

( SYSCON

)

END

SENSOR

REC

SAFETY

CTL

AMP

OUT

TO

D.

F

F

CN2001

2

1

LSA

SYN_IN

LPF

VIDEO

SECTION

( ON

SCREEN

)

V

T

O

OSD

V

FR

OM

OSD

V

.

PULSE

V

.

PULSE

VIDEO/N.

A

UDIO

VIDEO

ENV

VIDEO

ENV

X3001

CLOCK

SYSTEM

MAIN

END

SENSOR

RESET

SW

SAFETY

REC

S3001

SD

A

SCL

5

6

( SYSTEM

CONTR

OL

MICR

O

PR

OCESSOR

)

IC3001

LSB

LSA

LSC

TP4001

CTL.

P

3

0

M

LSB

LSC

LSD

ENCODER

RO

TA

R

Y

1

2

CN1

HEAD (+)

CTL

HEAD (-)

CTL

HEAD

HEAD

A/C

I2C

D

A

TA

A/V

I2C

CLK

A/V

S-SUB

TO

17

18

23

24

50

49

47

I2C

D

A

TA

A/V

I2C

CLK

A/V

D.

F

F

76

75

74

37

38

X

OUT

XI

N

Q3002

25

RESET

D3005

AL5.8V

SYS

IC3003

I2C

D

A

TA

I2C

CLK

I2C

D

A

TA

I2C

CLK/TEST

IC3004

( SERIAL

MEMOR

Y

)

43

27

A.MUTE(H)

14

FULL.E_ON(H)

N.REC_ST(H)

N.REC(H)

N.REC(H)

N.REC_ST(H)

A.MUTE(H)

A.MUTE

( H

)

TO

VIDEO/N.

A

UDIO

WF5

WF6

T

O

FMA/DEMOD

TO

TERMINAL

CAP

.M

FG

CAP

.M

F/R

CAP

.M

VCTL

LM

F/R/S

DR

UM

PG/FG

DR

UM

VCTL

68

62

33

61

65

34

22

JSA

86

JSB

87

64

78

31

H.REC_ST(H)

H.REC_ST(H)

28

A.FF

A.FF

26

A.ENV/ND(L)

A.ENV/ND(L)

81

32

15

20

CTL2

CTL3

SP_SHOR

T(H)

EP_SHOR

T(H)

19

T

O AD

V

. JOG

CN7003

V_T

O OSD

VIDEO_OUT

WF3

WF4

83

93

92

LSD

94

91

JS3001

4

3

2

5

6

1

4

9

10

11

12

12

2

1

12

10

4

11

9

1

DR

UM

MO

T

OR

58

57

3i

n1M

D

A

/

CAP

MO

T

OR

55

LO

ADING

MO

TOR

M

M

D

PG+

D

PG-

L1

L2

CAP

.M

FG

CAP

.M

F/R

CAP

.M

VCTL

LM

F/R/S

DR

UM

PG/FG

DR

UM

VCTL

CN3001

WF1

WF2

PHO

T

O

SENSOR

PHO

T

O

SENSOR

PC3001

PC3002

1

2

SP

FG

TU

FG

I2C_CLK_A/V

I2C_D

A

TA_A

V

I2C_CLK_A

V

I2C_D

A

TA_A

V

TO

S.

S

U

B

S3002

S

.CASSETTE SW

S

.CASSETTE

1

3

CN7001

JSA

JSB

S

.CASS(H)

TO

FMA/DEMOD

5

V_FR

OM_OSD

CTL1

11

CN501

12

5

0

3D DIGIT

AL/2M

11

CN1401

12

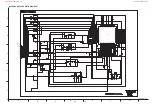

Note:F

or the w

a

v

ef

or

ms in this schematic diag

ram,ref

er to page 2-30.

SYSTEM CONTROL BLOCK DIAGRAM

www.freeservicemanuals.info

World of Free Manuals