SE7500CW2 Server Board Technical Product Specification

System BIOS

51

Revision 1.40

as described in this section, may be different from those observed on any one pre-production

version of the system BIOS. This section will be updated in the 1.0 release of this document.

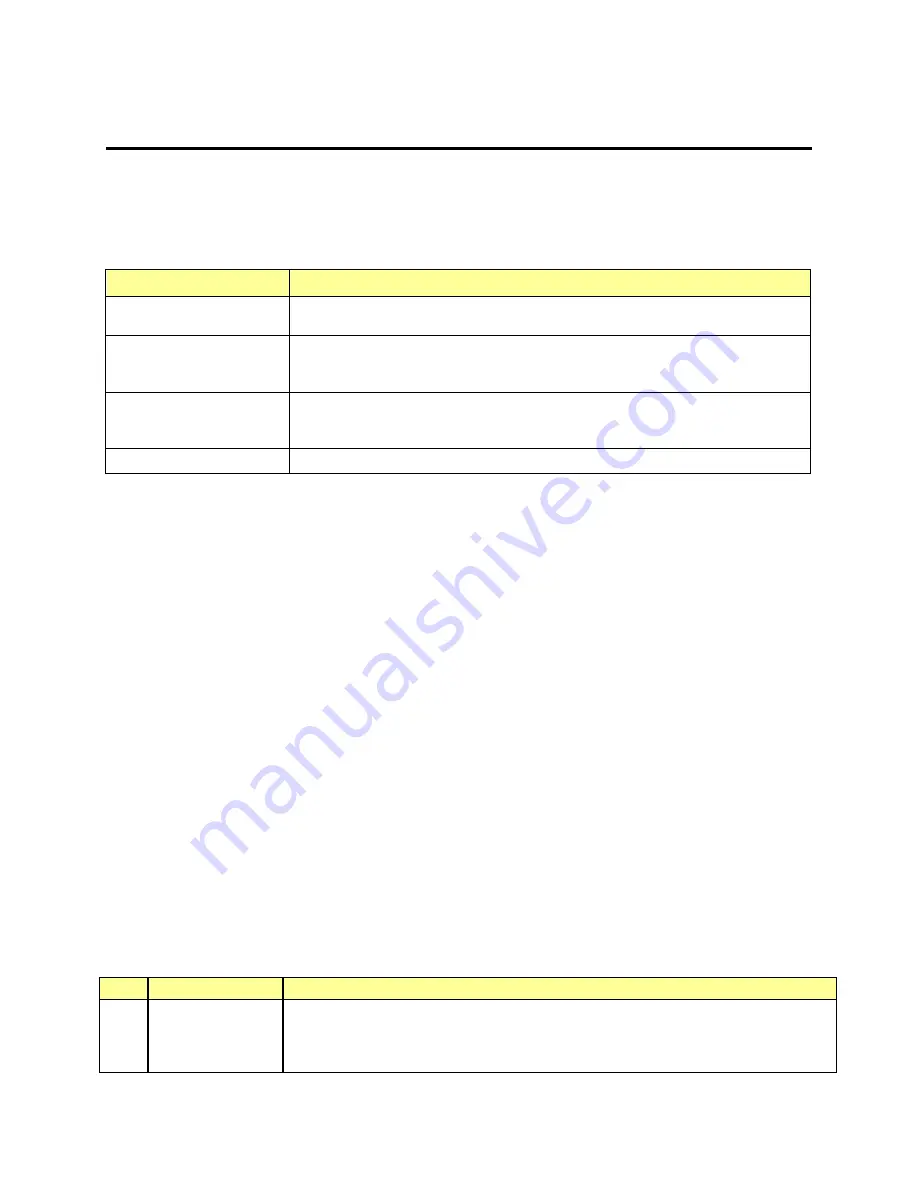

The BIOS Setup utility screen is divided into four functional areas. Table 15 describes each area:

Table 15: Setup Utility Screen

Functional Area

Description

Keyboard Command Bar

Located at the bottom of the screen or as part of the help screen. This bar displays

the keyboard commands supported by the setup utility.

Menu Selection Bar

Located at the top of the screen. Displays the various major menu selections

available to the user. The Server Setup utility major menus are: Main Menu,

Advanced Menu, Security Menu, Boot Menu, System Menu and the Exit Menu.

Options Menu

Each Option Menu occupies the left and center sections of the screen. Each menu

contains a set of features. Selecting certain features within a major Option Menu

drops you into sub-menus.

Item Specific Help Screen

An item-specific Help screen is located at the right side of the screen .

6.5.2

Entering the BIOS Setup Utility

During the BIOS POST operation, the user is prompted to use the F2 function key to enter Setup

as follows:

Press <F2> to enter Setup

A few seconds might pass before Setup is entered. This is the result of POST completing test

and initialization functions that must be completed before Setup can be entered. When Setup is

entered, the Main Menu options page is displayed.

6.5.3

Keyboard Command Bar

The bottom portion of the Setup screen provides a list of commands that are used to navigate

through the Setup utility. These commands are displayed at all times.

Each menu page contains a number of configurable options and/or informational fields.

Depending on the level of security in affect, configurable options may or may not be changed. If

an option cannot be changed due to the security level, its selection field is made inaccessible.

The Keyboard Command Bar supports the following:

Table 16: Keyboard Commands

Key

Option

Description

Enter Execute Command

The Enter key is used to activate sub-menus when the selected feature is a sub-menu,

or to display a pick list if a selecte d option has a value field, or to select a sub-field for

multi -valued features like time and date. If a pick list is displayed, the Enter key will undo

the pick list, and allow another selection in the parent menu.