3

Introduction

The objective of this reference design is to enable transceiver (XCVR) toolkit usage demonstration via Cyclone

10 GX development kit board. This user guide documentation will assist user to use XCVR toolkit to perform

XCVR channel bit error rate (BER) check via on board XCVR TX channel to RX channel loopback test and serial

loopback test in step by step guidance. BER is a typical measurement parameter used to inspect and build the

confidence level of the signal integrity quality of XCVR channel in industry. This reference design utilizes one

ATXPLL IP to clock one XCVR NativePHY IP 1.25Gbps XCVR duplex channel.

Requirement

The reference design requires the following hardware and software to run the hardware test:

•

Quartus® Prime Software Version: 17.1.1 Pro Edition

•

Cyclone 10 GX Development Kit Board

https://www.altera.com/products/boards_and_kits/dev-kits/altera/cyclone-10-gx-development-

•

FPGA Mezzanine Card (FMC) loopback card

Theory of Operation

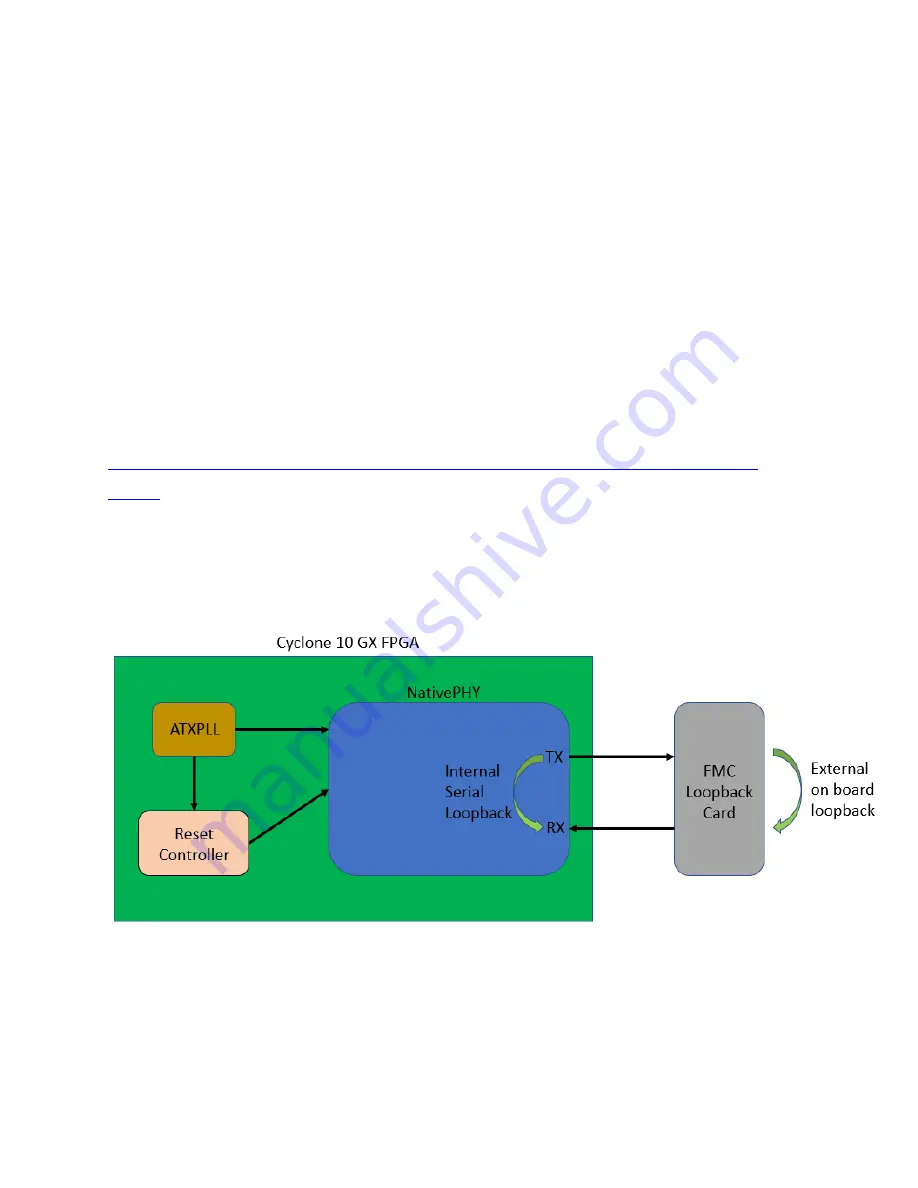

Figure 1. Block diagram of modules in the reference design

Figure 1 shows the high-level modules in the reference design as well as the interfaces among the

modules. The Cyclone 10 GX XCVR NativePHY IP is used to generate one 1.25Gbps XCVR duplex channel. The XCVR

Reset Controller IP is used to perform the reset to the XCVR channel and ATXPLL. The ATXPLL IP serves as XCVR PLL

to provide clock source to NativePHY IP XCVR channel.