314

Intel

®

855GME Chipset and Intel

®

6300ESB ICH Embedded Platform Design Guide

Layout Checklist

13.3.3

IDE Interface Layout Checklist

13.3.4

USB 2.0 Layout Checklist

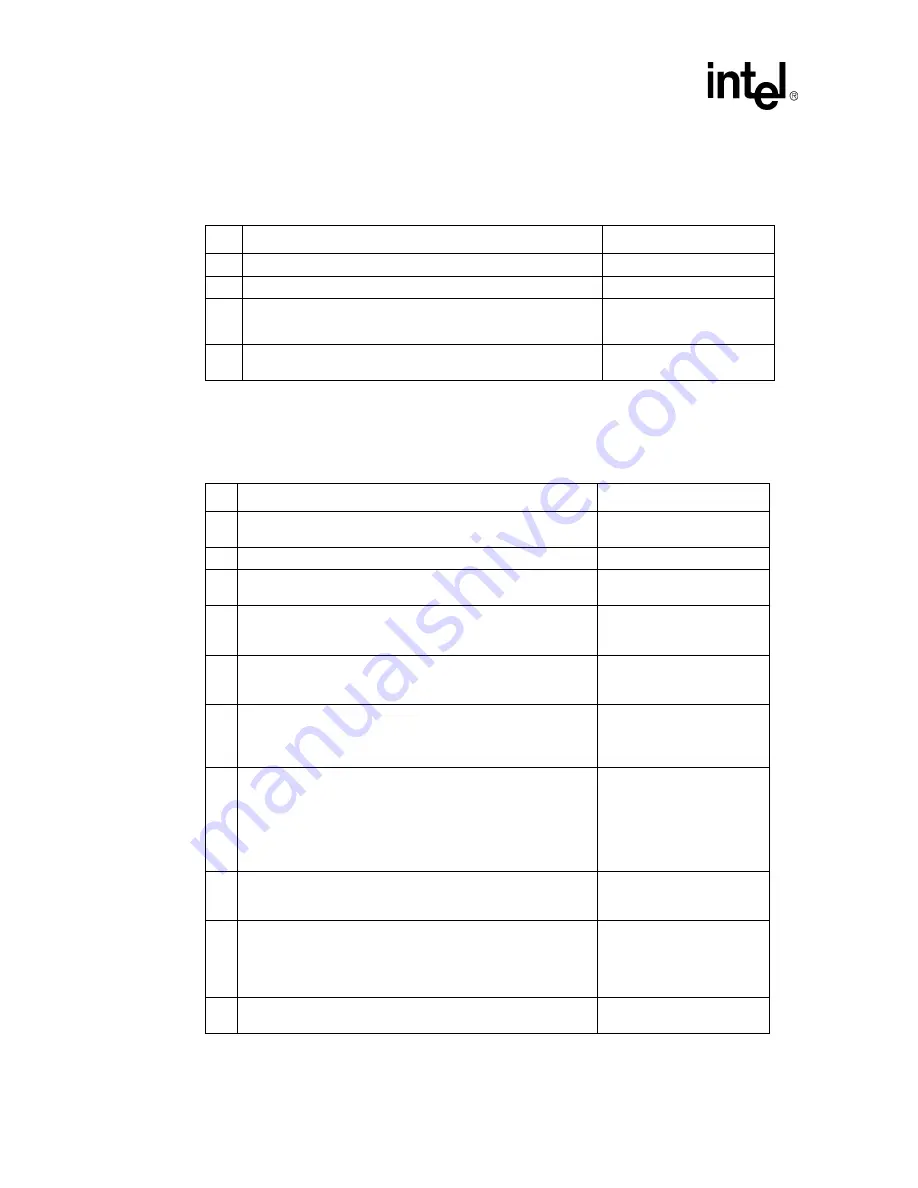

Table 152.

IDE Interface Layout Checklist

#

Layout Recommendations

Comments

1

Traces need to be routed 5 mils wide and 7 mils spaces

2

Max trace length is eight inches long.

3

The two strobe signals must be matched within 100 mils of each

other. The data lines must be within ± 500 mils of the average

length of the two strobe signals.

4

If series resistors are used, they should be placed close to the IDE

connector.

Table 153.

USB 2.0 Layout Checklist (Sheet 1 of 2)

#

Layout Recommendations

Comments

1

With minimum trace lengths, route high-speed clock and USB

differential pairs first.

2

Route USB signals ground referenced.

3

Route USB signals using a minimum of vias and corners. This

reduces signal reflections and impedance changes.

4

When it becomes necessary to turn 90°, use two 45° turns or an

arc instead of making a single 90° turn. This reduces reflections

on the signal by minimizing impedance discontinuities.

5

Do not route USB traces under crystals, oscillators, clock

synthesizers, magnetic devices or ICs that use and/or duplicate

clocks.

6

Stubs on USB signals should be avoided, as stubs will cause

signal reflections and affect signal quality. When a stub is

unavoidable in the design, the sum of all stubs on a given data

line should not be greater than 200 mils.

7

Route all traces over continuous planes (GND) with no

interruptions. Avoid crossing over anti-etch when possible.

Crossing over anti-etch (plane splits) increases inductance and

radiation levels by forcing a greater loop area. Likewise, avoid

changing layers with high-speed traces. (Applies to USB signals,

high-speed clocks, as well as slower signals that might be

coupling to them.)

8

Keep USB signals clear of the core logic set. High current

transients are produced during internal state transitions, which

may be difficult to filter out.

9

Keep traces at least 90 mils away from the edge of the plane (V

CC

or GND depending on which plane to which the trace is routed).

This helps prevent the coupling of the signal onto adjacent wires

and helps prevent free radiation of the signal from the edge of the

PCB.

10

Maintain parallelism between USB differential signals with the

trace spacing needed to achieve the target differential impedance.

Summary of Contents for 6300ESB ICH

Page 24: ...24 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide Introduction...

Page 102: ...102 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide...

Page 122: ...122 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide...

Page 190: ...190 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide Hub Interface...

Page 318: ...318 Intel 855GME Chipset and Intel 6300ESB ICH Embedded Platform Design Guide Layout Checklist...