XC164CM

XC164CM Board

Memory Models

XC164CM series Board Manual

18

V 1.0, 2006-01

4

Memory Models

The memory space of the XC164CM is configured in a “von Neumann” architecture. This

means that code and data are accessed within the same linear address space.

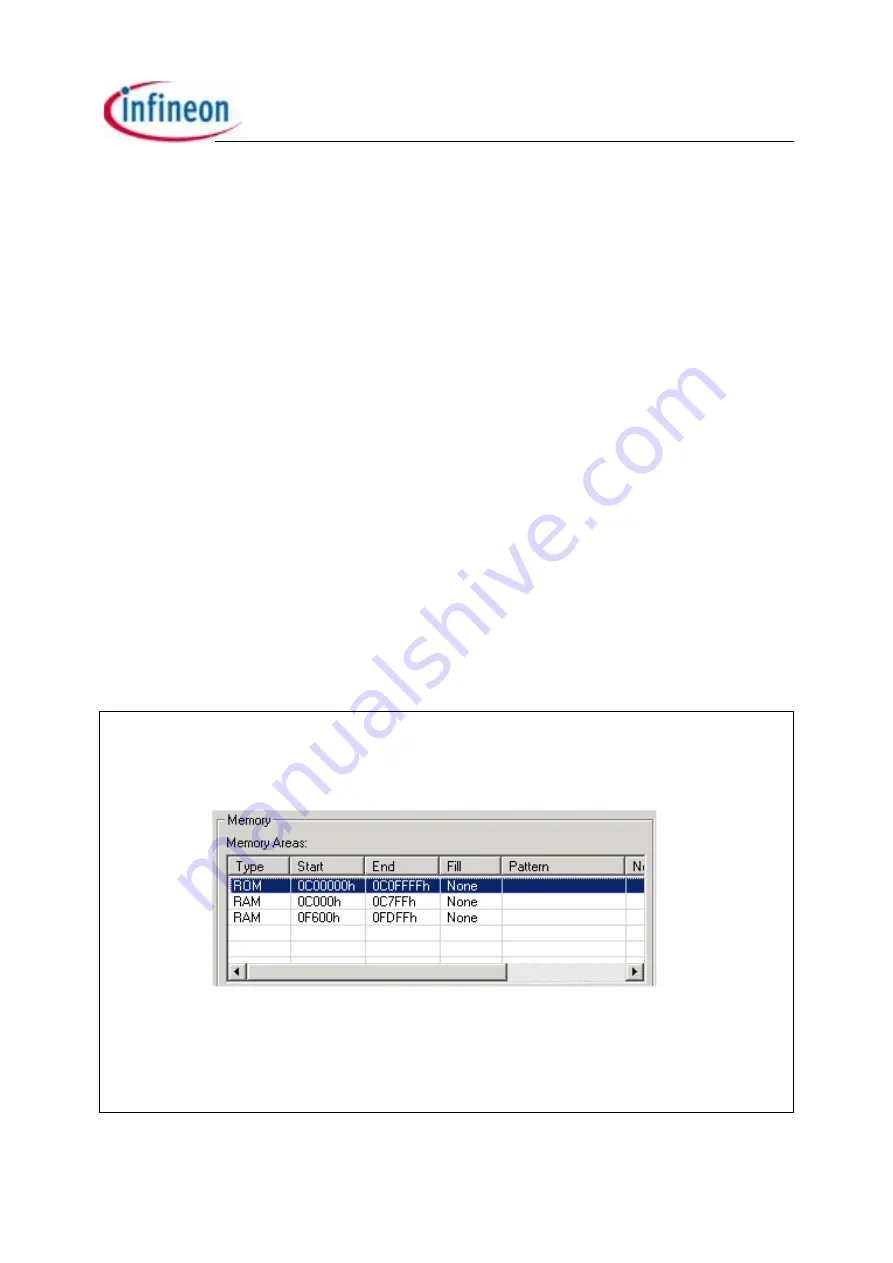

Attached there are two examples for memory mapping of the XC164CM Board.

4.1

Internal Flash

The XC164CM incorporates 64 Kbytes of embedded Flash memory (starting at location

C0’0000H) for code or constant data. It is operated from the 5 V pad supply and requires

no additional programming voltage. The Flash array is organized in five sectors of 4 × 8

Kbytes, and 1 × 32 Kbytes1). It combines the advantages of very fast read accesses with

protected but simple writing algorithms for programming and erasing. The 64-bit code

read accesses realize maximum CPU performance by fetching two double word

instructions (or four single word instructions) in a single access cycle.

Data integrity is enhanced by an error correction code enabling dynamic correction

ofsingle bit errors. Additionally, special margin checks are provided to detect and correct

problematic bits before they lead to actual malfunctions.

The On-chip programming can be done either with a utility program, so called “Memtool”

or with several other Toolchains of our Tool vendors. Memtool is using the ASC

bootstrap Loader. The latest version can be found on the Infineon web side. Other tools

are using the OCDS interface.

Figure 7

Example for memory mapping (internal flash)