CY8CKIT-064S0S2-4343W PSoC 64 Standard Secure – AWS Wi-Fi BT Pioneer Kit Guide, Doc. # 002-30680 Rev. *B

43

Hardware

4.2.9

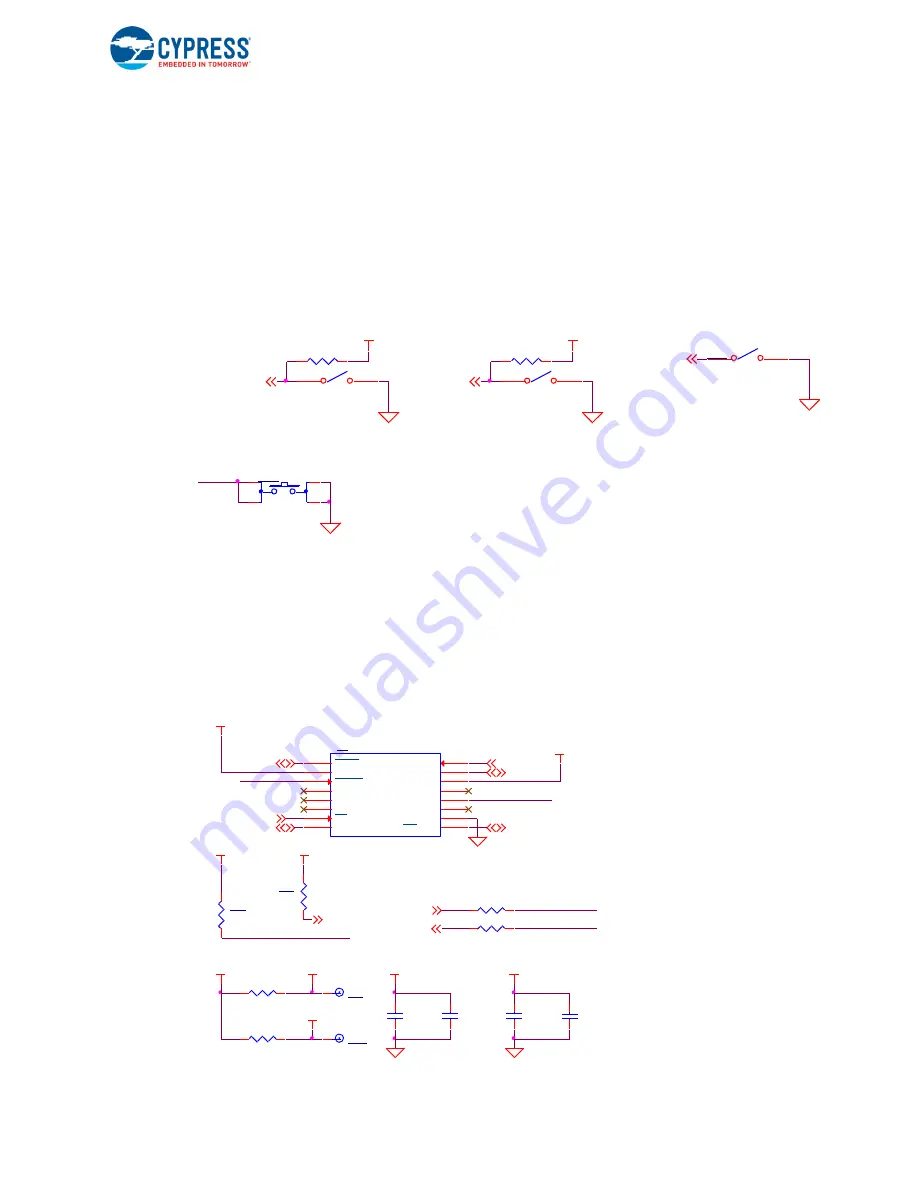

Push Buttons

The board has a reset button, two user-controllable buttons and a KitProg3 Mode selection button.

The reset button (

SW1

) is connected to the XRES pin of the PSoC 64 MCU and is used to reset the

device. Two user buttons (

SW2

and

SW4

) are connected to pin P0[4] and P1[4] of the PSoC 64

MCU respectively. In addition, the Mode selection button (

SW3

) is connected to the PSoC 5LP

device for programming mode selection (Refer to the

are active LOW configuration and short to GND when pressed. The CY8CMOD-064S0S2-4343W

has a pull-up on the PSoC 64 MCU XRES line.

Figure 4-13. Schematics of Push Buttons

4.2.10

Cypress Quad SPI NOR Flash

The PSoC 64 Standard Secure – AWS Wi-Fi BT Pioneer Board has a Cypress NOR flash memory

(S25FL512SAGMFI010) of 512Mb capacity. The NOR flash is connected to the Quad SPI interface

of the PSoC 64 MCU device. The NOR flash device can be used for both data and code with

execute-in-place (XIP) support and encryption.

Figure 4-14. Schematics of QSPI Flash

SW4

EVQ-PNF04M

SW2

EVQ-PNF04M

USER_BTN_1

R20

10K

User Button / Hibernate Wakeup

VBACKUP

USER_BTN_2

VDDD

R110

10K

SW1

EVQ-PE105K

Reset Button

XRES_L_MCU

SW3

SKRPACE011

1

4

2

3

P5LP1_2

Mode Switch

R90

0 OHM

C54

0.1uF

16V

C32

0.1uF

16V

C56

1uF

10V

R26

0 OHM

C55

1uF

10V

VCC_IO_FLASH

VCC_FLASH

VCC_IO_FLASH

VCC_FLASH

VCC_VDDIO0

Quad SPI Flash Memory Section

R107

0 OHM

No Load

IO6

FLASH_RST_L

FLASH_SS_L

TP9

TP20

U3

S25FL512SAGMFI010

HOLD /IO3

1

VCC

2

RESET /RFU

3

DNU_1

4

DNU_2

5

DNU_3

6

CS

7

SO/IO1

8

WP /IO2

9

VSS

10

DNU_4

11

DNU_5

12

DNU_6

13

DNU_7

14

SI /IO0

15

SCK

16

FLASH_INT_L

FLASH_SS_L

IO5

QSPI_IO1

QSPI_IO0

QSPI_SCK

QSPI_IO3

QSPI_IO2

R138

0 OHM

No Load

FLASH_INT_L

FLASH_INT_L

FLASH_RST_L

R93

10K

VCC_IO_FLASH

R92

10K

No Load

VCC_IO_FLASH

VCC_FLASH

VCC_IO_FLASH