08/23/15

11

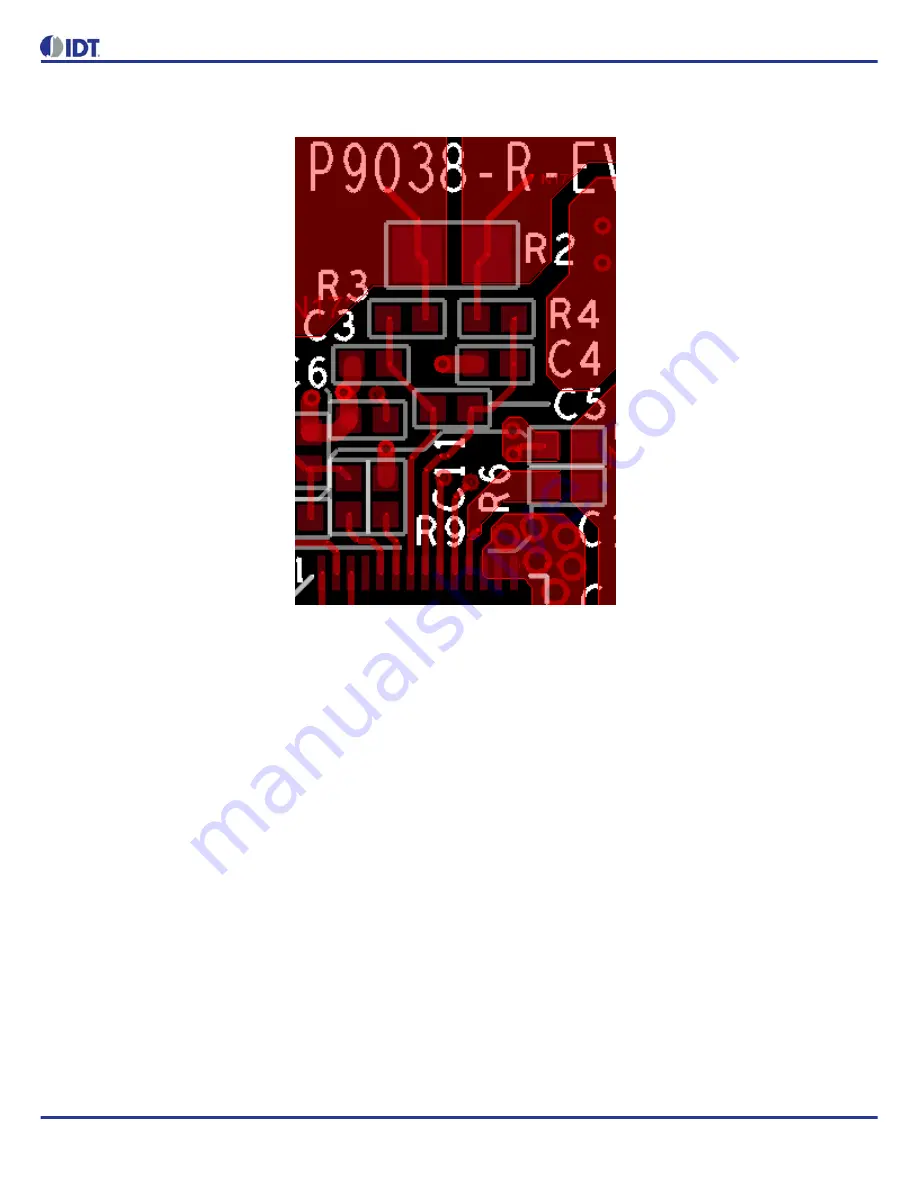

P9038 LAYOUT GUIDE

AN-894

Figure 9. Kelvin Connections to Rsns (R40)

The Input power connections and traces should be routed with adequate width to conduct up to 2 A of DC current with minimal

voltage losses. When using the USB and N-CH FET, a device with an acceptable and minimal RDSON specification should be

selected.

The High Current Power GND will carry the DC input current up to ~ 1.7 A, including the input ripple current at the power transfer

frequency. As a result, it may be prone to varying voltage drops depending on the Rx load and is not recommended to be

common to sensitive GND for DEMOD signals. The Noisy PGND area will have high current switching and rapid voltage changes

induced from the full bridge inverter switching, this area is not suitable to be used for GND reference. The DEMOD circuits GND

connections should be made away from the PGND pins and have a separate current return path to the EPAD from the input

capacitors and the PGND pins.

Next, the LDO input capacitors need to be placed in close proximity to the P9038 device. The P9038 has two Low Drop-Out

(LDO) linear voltage regulators: LDO5V (Pin 19), LDO2P5V (Pin 20). The LDO5V output and LDO2P5V input may share a single

1µF ceramic capacitor for cost reduction or compact designs. Both LDO input and output capacitors should be placed near each

respective LDO pin with the GND plate of the capacitor connected to the EPAD GND area of the PCB. While the LDO's are

technically power circuits, they are sensitive to noise and should not be placed far from the P9038 device to promote stable and

reliable operation.

EPAD

The use of a grid of 25 thermal vias placed inside the E-PAD of the P9038 device is recommended. Using thermal vias and

having one or more GND planes in direct contact is crucial for optimal thermal performance. Typical thermal via diameter is

0.3mm and spacing should be 1mm pitch. The land pattern drawing can be found in the product datasheet.