IDT Installation of the EB4T4 Eval Board

EB4T4 Eval Board Manual

2 - 6

August 20, 2007

Notes

• The host system board IO Controller Hub asserting PERST# signal, which propagates through

the PCIe upstream edge connector of the EB4T4. Note that one can bypass the onboard voltage

monitor (TLC7733D) by moving the shunt from pin 1-2 to pin 2-3 (default) on W2.

Both events cause the onboard voltage monitor (TLC7733D) to assert the PCI Express Reset

(PERSTN) input of the PES4T4 while power is on.

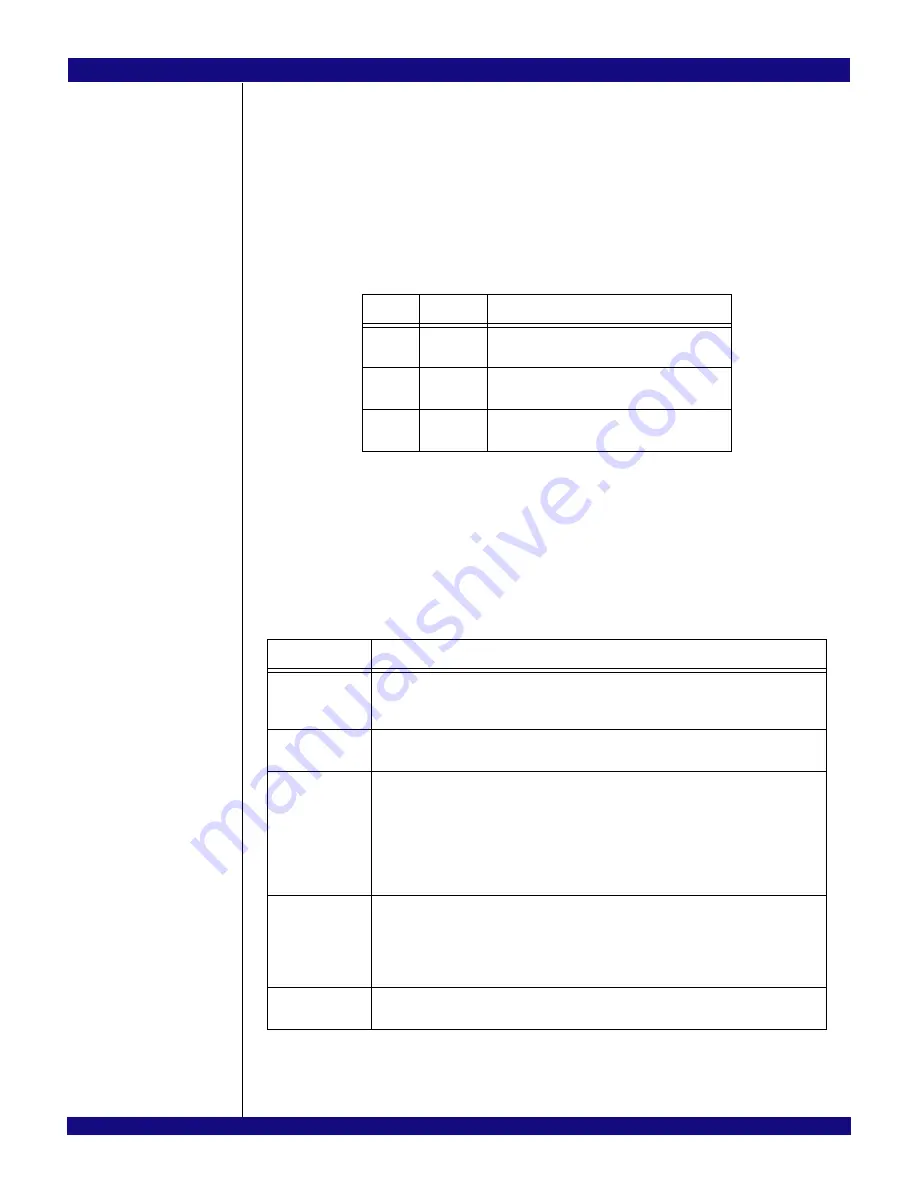

Downstream Reset

The PES4T4 provides a a choice of either a software-controlled reset for each downstream port through

GPIO pins or a fundamental reset through PERST#. Selection is made by jumpers described in Table 2.4.

Boot Configuration Vector

A boot configuration vector consisting of the signals listed in Table 2.5 is sampled by the PES4T4 during

a fundamental reset (while PERSTN is active). The boot configuration vector defines the essential parame-

ters for switch operation and is set using DIP switches S3 and S5 as defined in Table 2.6.

Port # Jumper

Selection

4

W9

[1-2] Software controlled reset through GPIO1

[2-3] Fundamental reset PERST# (default)

3

W6

[1-2] Software controlled reset through GPIO9

[2-3] Fundamental reset PERST# (default)

2

W7

[1-2] Software controlled reset through GPIO0

[2-3] Fundamental reset PERST# (default)

Table 2.4 Downstream Reset Selection

Signal

Description

CCLKDS

Common Clock Downstream.

When the CCLKDS pin is asserted, it indicates that a com-

mon clock is being used between the downstream device and the downstream port.

Default: 0x1

CCLKUS

Common Clock Upstream.

When the CCLKUS pin is asserted, it indicates that a common

clock is being used between the upstream device and the upstream port.

Default: 0x1

RSTHALT

Reset Halt.

When this signal is asserted during a PCI Express fundamental reset, the

PES4T4 executes the reset procedure and remains in a reset state with the Master SMBus

active. This allows software to read and write registers internal to the device before normal

device operation begins. The device exits the reset state when the RSTHALT bit is cleared

in the P0_SWCTL register through the SMBus.

The value may be overridden by modifying the RSTHALT bit in the P0_SWCTL register.

Default: 0x0

SWMODE[2:0]

Switch Mode.

These configuration pins determine the PES4T4 switch operating mode.

Default: 0x1

0x0 - Normal switch mode

0x1 - Normal switch mode with Serial EEPROM-based initialization

0x2 through 0x8 - Reserved

APWRDIS#

Auxiliary Power Disable.

When this pin is active, it disables the device from using auxil-

iary power supply.

Default: 0x0

Table 2.5 Boot Configuration Vector Signals

Summary of Contents for EB4T4 Eval Board

Page 4: ...IDT Table of Contents EB4T4 Eval Board Manual ii August 20 2007 Notes...

Page 6: ...IDT List of Tables EB4T4 Eval Board Manual iv August 20 2007 Notes...

Page 8: ...IDT List of Figures EB4T4 Eval Board Manual vi August 20 2007 Notes...

Page 24: ...IDT Software for the EB4T4 Eval Board EB4T4 Eval Board Manual 3 2 August 20 2007 Notes...

Page 25: ...Notes EB4T4 Eval Board Manual 4 1 August 20 2007 Chapter 4 Schematics Schematics...