10. Reset and Clocking > Clocking

90

PEB383 User Manual

July 25, 2011

Integrated Device Technology, Inc.

Confidential - NDA Required

10.2

Clocking

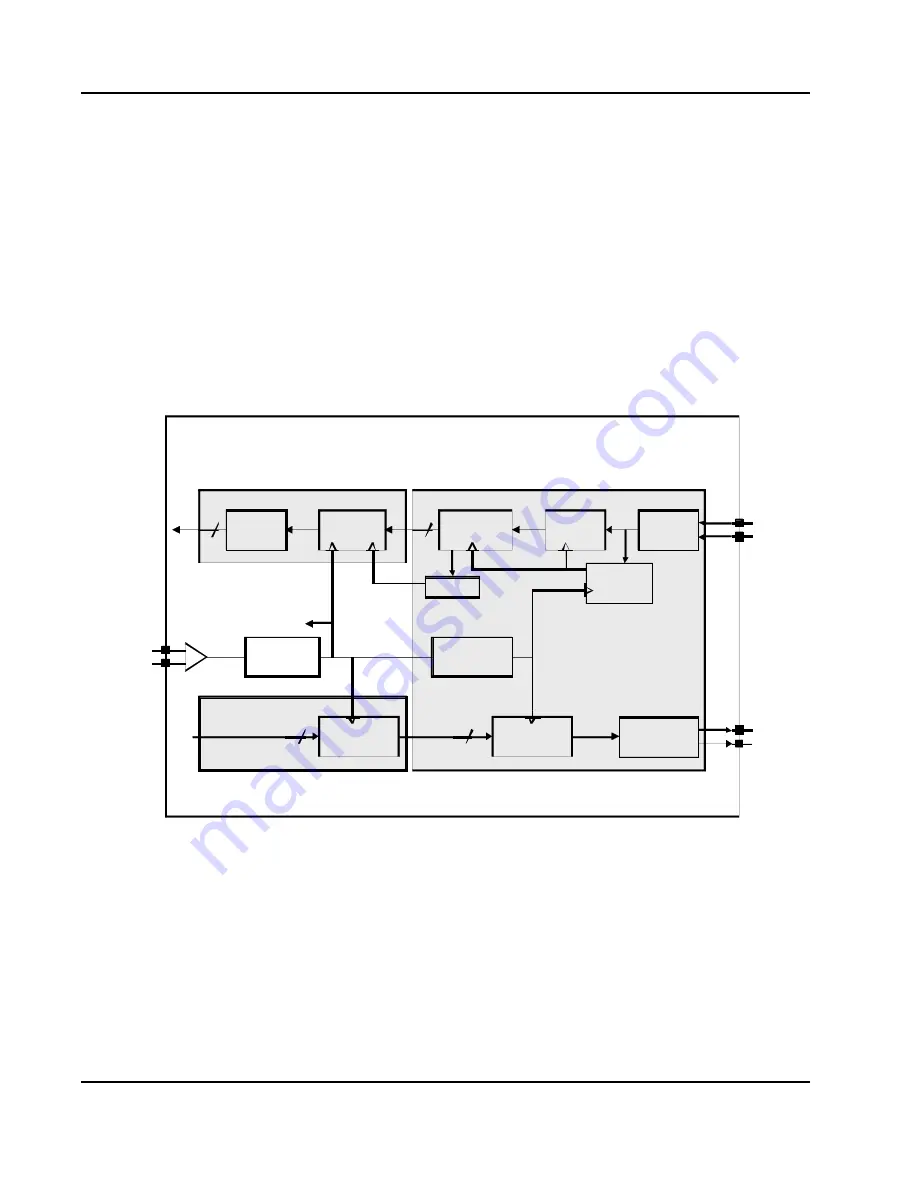

This section discusses clocking information for the PEB383’s PCIe and PCI Interfaces.

10.2.1

PCIe Clocking

The PCIe clocking is shown in

. The 100-MHz reference clock, PCIE_REFCLK_n/p, drives a

x(5/4) PLL to create a 125-MHz clock. The 125-MHz clock is further multiplied to create the Tx

parallel to serial conversion, and clocking out the Tx pins, PCIE_TXD_n/p (The receive data is clocked

into the PEB383 with the recovered clock. The elastic buffer operates on the recovered byte clock

(from K28.5) and the internal generated 125-MHz clock. The two clocks can vary by twice the ppm

tolerance of the reference clock tolerance on any one device (300ppm). Buffer overflow is prevented

by discarding skip characters.

Figure 26: PCIe Clocking

PCS

PHY

PCS

PCI E_REFCLK_p

PCI E_REFCLK_n

P LL

x(5/4)

8b10b encode

Parallel t o serial

Tx Diff erential

Driver

PCI E_TXD_p

PCI E_TXD_n

100 MHz

125 MHz

P LL

x20

2.5 GHz

Rx Diff erential

Rec eiv er

PCI E_RXD_p

PCI E_RXD_n

Cloc k recovery

Data rec ov ery

s erial to Parall el

Elas tic buf fer

Rec ov ered 2.5 GHz

10b8b decode

K 28.5

16

20

20

16

125 MHz (t o PCI e core)