4-1 RECEIVER CIRCUITS

4-1-1 ANTENNA SWITCHING CIRCUIT

The antenna switching circuit functions as a low-pass filter

while receiving and a resonator circuit while transmitting.

This circuit does not allow transmit signals to enter the

receiver circuits.

Received signals enter the antenna connector (CHASSIS;

MP44) and pass through the low-pass filter (L1, L2, C1, C2,

C420). The filtered signals are passed through the

λ

⁄

4

type

antenna switching circuit (D25, L39, D24) and then applied

to the RF circuit.

4-1-2 RF CIRCUIT

The RF circuit amplifies signals within the range of frequen-

cy coverage and filters out-of-band signals.

The signals from the antenna switching circuit pass through

the tunable bandpass filter (D21, L37). The filtered signals

are amplified at the RF amplifier (Q20) and then passed

through the another three-stage bandpass filters (D20–D18,

L36, L34, L33) to suppress unwanted signals. The filtered

signals are applied to the 1st mixer circuit.

D18–D21 employ varactor diodes, that are controlled by the

CPU via the D/A converter (IC27), to track the bandpass fil-

ter. These varactor diodes tune the center frequency of an

RF pass band for wide bandwidth receiving and good image

response rejection.

4-1-3 1ST MIXER AND 1ST IF CIRCUITS

The 1st mixer circuit converts the received signal into fixed

frequency of the 1st IF signal with the PLL output frequency.

By changing the PLL frequency, only the desired frequency

passes through a monolithic filter at the next stage of the 1st

mixer.

The RF signals from the bandpass filter are mixed with the

1st LO signals, where come from the RX VCO circuit via the

attenuator (R108–R106), at the 1st mixer circuit (Q19) to

produce a 47.25 MHz 1st IF signal. The 1st IF signal is

passed through a monolithic filter (FI1) in order to obtain

selection capability and to pass only the desired signals. The

filtered signal is applied to the 2nd IF circuit after being

amplified at the 1st IF amplifier (Q18).

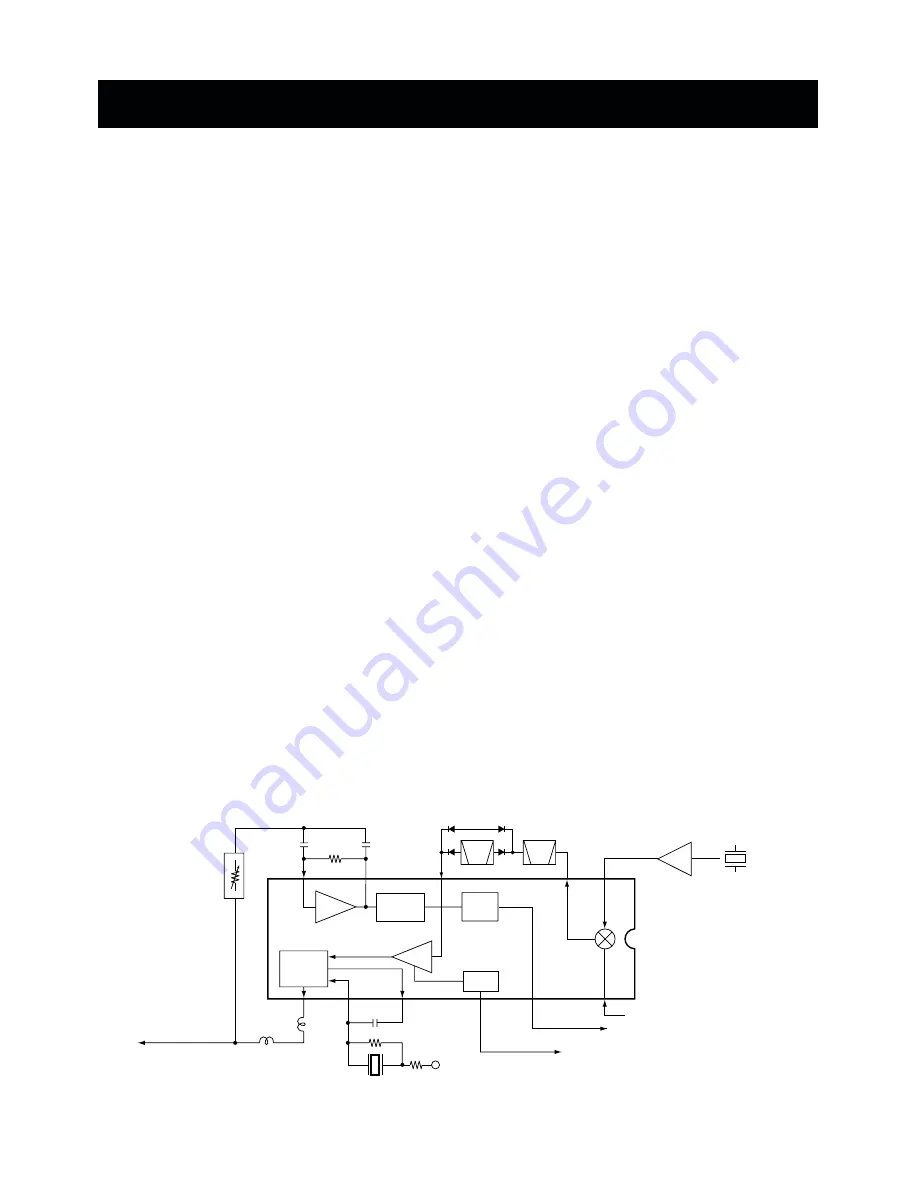

4-1-4 2ND IF AND DEMODULATOR CIRCUITS

The 2nd mixer circuit converts the 1st IF signal into a 2nd IF

signal. The double-conversion superheterodyne system

(which convert receive signals twice) improves the image

rejection ratio and obtains stable receiver gain.

The 1st IF signal from the IF amplifier (Q18) is applied to the

2nd mixer section of the FM IF IC (IC3, pin 16), and is mixed

with the 2nd LO signal to be converted into a 450 kHz 2nd

IF signal.

The FM IF IC (IC3) contains the 2nd mixer, 2nd local oscil-

lator, limiter amplifier, quadrature detector, active filter and

noise amplifier circuits. A 2nd LO signal (46.8 MHz) is pro-

duced at the PLL circuit by tripling it’s reference frequency

(15.6 MHz).

The 2nd IF signal from the 2nd mixer (IC3, pin 3) passes

through the ceramic filters (FI2, FI3) during narrow channel

spacing selection or FI2 only (bypassing FI3) during wide

channel spacing selection to remove unwanted heterodyned

frequencies. It is then amplified at the limiter amplifier sec-

tion (IC3, pin 5) and applied to the quadrature detector sec-

tion (IC3, pins 10, 11) to demodulate the 2nd IF signal into

AF signals.

The demodulated AF signals are output from pin 9 (IC3) and

applied to the AF circuit via the receiver mute circuit.

4 - 1

SECTION 4

CIRCUIT DESCRIPTION

• 2nd IF and demodulator circuits

Mixer

16

Limiter

amp.

2nd IF filter

450 kHz

X1

15.6 MHz

46.8 MHz

IC3 TA31136FN

12

1st IF from the IF amplifier (Q18)

"RSSI" signal to the CPU (IC14, pin 50)

11

10

9

8

7

AF signal "DSIN"

R5

X2

Squelch level

controller IC13

2

Active

filter

Noise

detector

FM

detector

13

"NOIS" signal to the CPU (IC14, pin 75)

RSSI

Noise

comp.

×

3

Tripler

Q15

23

24

FI2

5

FI3

3