10.12 Sector Number Register

This register contains the starting sector number for any disk data access for the subsequent command.

The sector number is from one to the maximum number of sectors per track.

In LBA mode, this register contains Bits 0–7. At the end of the command, this register is updated to reflect

the current LBA Bits 0–7.

10.13 Status Register

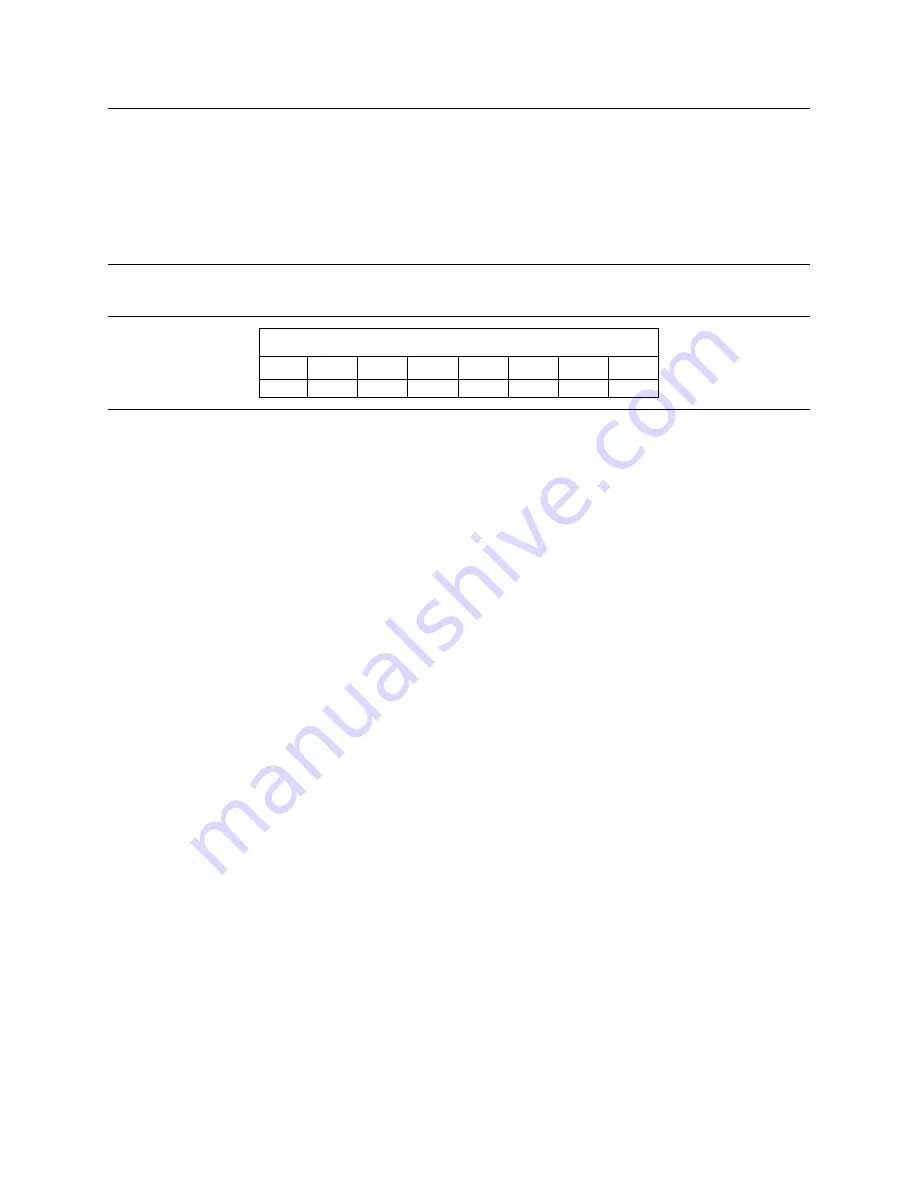

ERR

IDX

COR

DRQ

DSC

DF

DRDY

BSY

0

1

2

3

4

5

6

7

Status Register

Figure 56. Status Register

This register contains the device status. The contents of this register are updated whenever an error

occurs and at the completion of each command.

If the host reads this register when an interrupt is pending, it is considered to be the interrupt acknow-

ledge. Any pending interrupt is cleared whenever this register is read.

If BSY=1, no other bits in the register are valid.

Bit Definitions

Error. Bit ERR=1 indicates that an error occurred during execution of the previous com-

mand. The Error Register should be read to determine the error type. The device sets bit

ERR=0 when the next command is received from the host.

ERR

Index. Bit IDX=1 once per revolution. Since IDX=1, only for a very short time during each

revolution, the host may not see it set to 1 even if the host is reading the Status Register

continuously. Therefore the host should not attempt to use IDX bit for timing purposes.

IDX

Corrected Data. Always 0.

CORR (COR)

Data Request. Bit DRQ=1 indicates that the device is ready to transfer a word or byte of

data between the host and the device. The host should not write the Command register

when DRQ=1.

DRQ

Device Seek Complete. If DSC=1, it indicates that a Seek has completed and the device

head is settled over a track. Bit DSC is set to 0 by the device just before a Seek begins.

When an error occurs, this bit is not changed until the Status Register is read by the host

and at that time the bit again indicates the current Seek complete status. When the de-

vice enters into or is in Standby mode or Sleep mode, this bit is set by device in spite of

the drive not spinning up.

DSC

Device Fault. It DF=1 it indicates that the device has detected a write fault condition. Bit

DF is set to 0 after the Status Register is read by the host.

DF

Device Ready. When bit RDY=1 it indicates that the device is capable of responding to a

command. Bit RDY will be set to 0 during power on until the device is ready to accept a

command.

DRDY (RDY)

Busy. Bit BSY=1 whenever the device is accessing the registers. The host should not

read or write any registers when BSY=1. If the host reads any register when BSY=1, the

contents of the Status Register will be returned.

BSY

Travelstar 60GH & 40GN hard disk drive specifications

72

Summary of Contents for IC25N040ATCS04 - Travelstar 40 GB Hard Drive

Page 9: ...This page intentionally left blank...

Page 13: ...This page intentionally left blank...

Page 17: ...This page intentionally left blank...

Page 19: ...This page intentionally left blank...

Page 20: ...Part 1 Functional specification Travelstar 60GH 40GN hard disk drive specifications 7...

Page 21: ...This page intentionally left blank...

Page 23: ...This page intentionally left blank...

Page 31: ...This page intentionally left blank...

Page 35: ...This page intentionally left blank...

Page 73: ...This page intentionally left blank...

Page 74: ...Part 2 Interface specification Travelstar 60GH 40GN hard disk drive specifications 61...

Page 75: ...This page intentionally left blank...

Page 77: ...This page intentionally left blank...

Page 79: ...This page intentionally left blank...

Page 113: ...This page intentionally left blank...

Page 207: ...This page intentionally left blank...