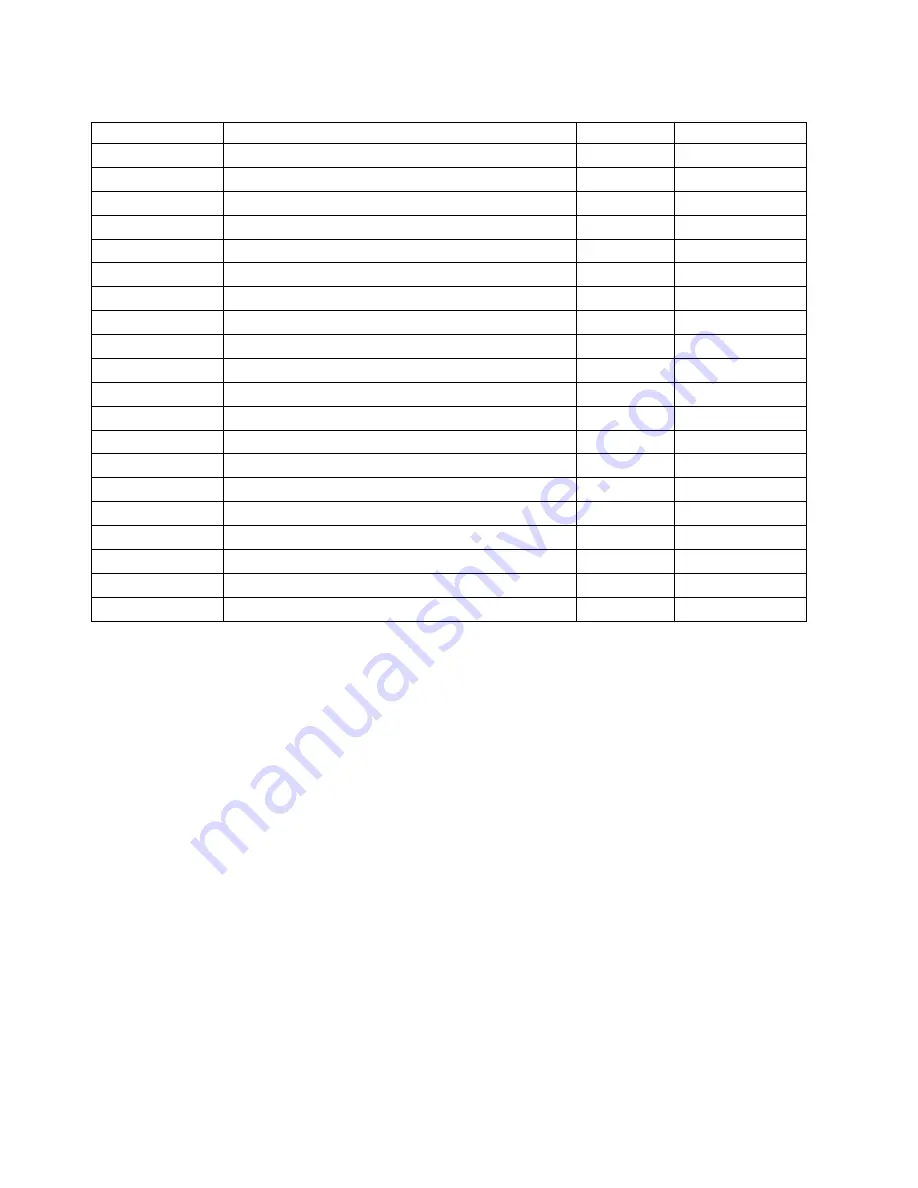

Table 3. DMA I/O address map (continued)

Address (hex)

Description

Bits

Byte pointer

008A

Channel 7, page table address register

00 – 07

008B

Channel 5, page table address register

00 – 07

008F

Channel 4, page table address/refresh register

00 – 07

00C0

Channel 4, memory address register

00 – 15

Yes

00C2

Channel 4, transfer count register

00 – 15

Yes

00C4

Channel 5, memory address register

00 – 15

Yes

00C6

Channel 5, transfer count register

00 – 15

Yes

00C8

Channel 6, memory address register

00 – 15

Yes

00CA

Channel 6, transfer count register

00 – 15

Yes

00CC

Channel 7, memory address register

00 – 15

Yes

00CE

Channel 7, transfer count register

00 – 15

Yes

00D0

Channels 4–7, read status/write command register

00 – 07

00D2

Channels 4–7, write request register

00 – 02

00D4

Channels 4–7, write single mask register bit

00 – 02

00D6

Channels 4–7, mode register (write)

00 – 07

00D8

Channels 4–7, clear byte pointer (write)

N/A

00DA

Channels 4–7, master clear (write)/temp (read)

00 – 07

00DC

Channels 4–7, clear mask register (write)

00 – 03

00DE

Channels 4–7, write all mask register bits

00 – 03

00DF

Channels 5–7, 8- or 16-bit mode select

00 – 07

66

User Guide

Summary of Contents for 6339

Page 1: ...User Guide Type 6339 6341 6342 6346 6347 6348 Type 2256 2257...

Page 2: ......

Page 5: ...iv User Guide...

Page 21: ...10 User Guide...

Page 39: ...28 User Guide...

Page 51: ...40 User Guide...

Page 65: ...54 User Guide...

Page 69: ...58 User Guide...

Page 73: ...62 User Guide...

Page 79: ...68 User Guide...

Page 84: ......