HT46R46/C46/R47/C47/R48A/C48A/R49

Rev. 1.41

23

December 30, 2008

As in the case of the other two modes, when the counter

is full and overflows, the timer will be reset to the value

already loaded into the preload register. If the timer in-

terrupt is enabled, an interrupt signal will also be gener-

ated. To ensure that the external pin PA4/TMR is

configured to operate as a pulse width measuring input

pin, two things have to happen. The first is to ensure that

the TM0 and TM1 bits place the timer/event counter in

the pulse width measuring mode, the second is to en-

sure that the port control register configures the pin as

an input. It should be noted that a timer overflow is one

of the wake-up sources.

Programmable Frequency Divider

-

PFD

The PFD output is pin-shared with the I/O pin PA3. The

PFD function is selected via configuration option, how-

ever, if not selected, the pin can operate as a normal I/O

pin. The timer overflow signal is the clock source for the

PFD circuit. The output frequency is controlled by load-

ing the required values into the timer prescaler registers

to give the required division ratio. The counter, driven by

the system clock which is divided by the prescaler value,

will begin to count-up from this preload register value

until full, at which point an overflow signal is generated,

causing the PFD output to change state. The counter

will then be automatically reloaded with the preload reg-

ister value and continue counting-up.

For the PFD output to function, it is essential that the

corresponding bit of the Port A control register PAC bit 3

is setup as an output. If setup as an input the PFD output

will not function, however, the pin can still be used as a

normal input pin. The PFD output will only be activated if

bit PA3 is set to

²

1

²

. This output data bit is used as the

on/off control bit for the PFD output. Note that the PFD

output will be low if the PA3 output data bit is cleared to

²

0

²

.

Using this method of frequency generation, and if a

crystal oscillator is used for the system clock, very pre-

cise values of frequency can be generated.

Prescaler

Bits PSC0~PSC2 of the TMRC register can be used to

define the pre-scaling stages of the internal clock

sources of the Timer/Event Counter. The Timer/Event

Counter overflow signal can be used to generate signals

for the PFD and Timer Interrupt.

I/O Interfacing

The Timer/Event Counter, when configured to run in the

event counter or pulse width measurement mode, re-

quire the use of the external PA4/TMR pin for correct op-

eration. As this pin is a shared pin it must be configured

correctly to ensure it is setup for use as a Timer/Event

Counter input and not as a normal I/O pin. This is imple-

mented by ensuring that the mode select bits in the

Timer/Event Counter control register, select either the

event counter or pulse width measurement mode. Addi-

tionally the Port Control Register PAC bit 4 must be set

high to ensure that the pin is setup as an input. Any

pull-high resistor configuration option on this pin will re-

main valid even if the pin is used as a Timer/Event

Counter input.

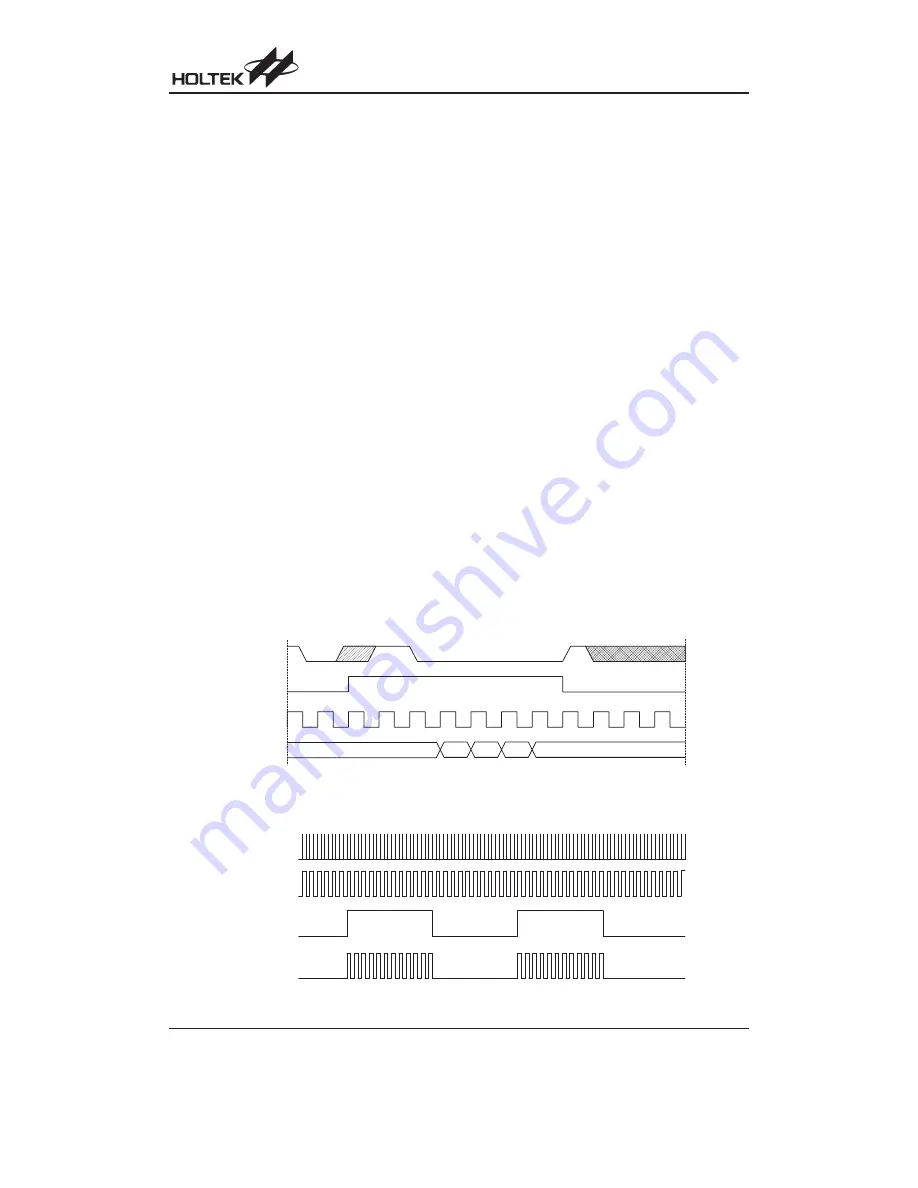

+ 1

+ 2

+ 3

+ 4

T i m e r

E x t e r n a l T M R

P i n I n p u t

T O N ( w i t h T E = 0 )

P r e s c a l e r O u t p u t

I n c r e m e n t

T i m e r C o u n t e r

P r e s c a l e r O u t p u t i s s a m p l e d a t e v e r y f a l l i n g e d g e o f T 1 .

Pulse Width Measure Mode Timing Chart

T i m e r O v e r f l o w

P F D C l o c k

P A 3 D a t a

P F D O u t p u t a t P A 3

PFD Output Control