5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

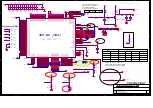

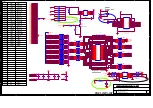

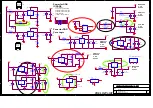

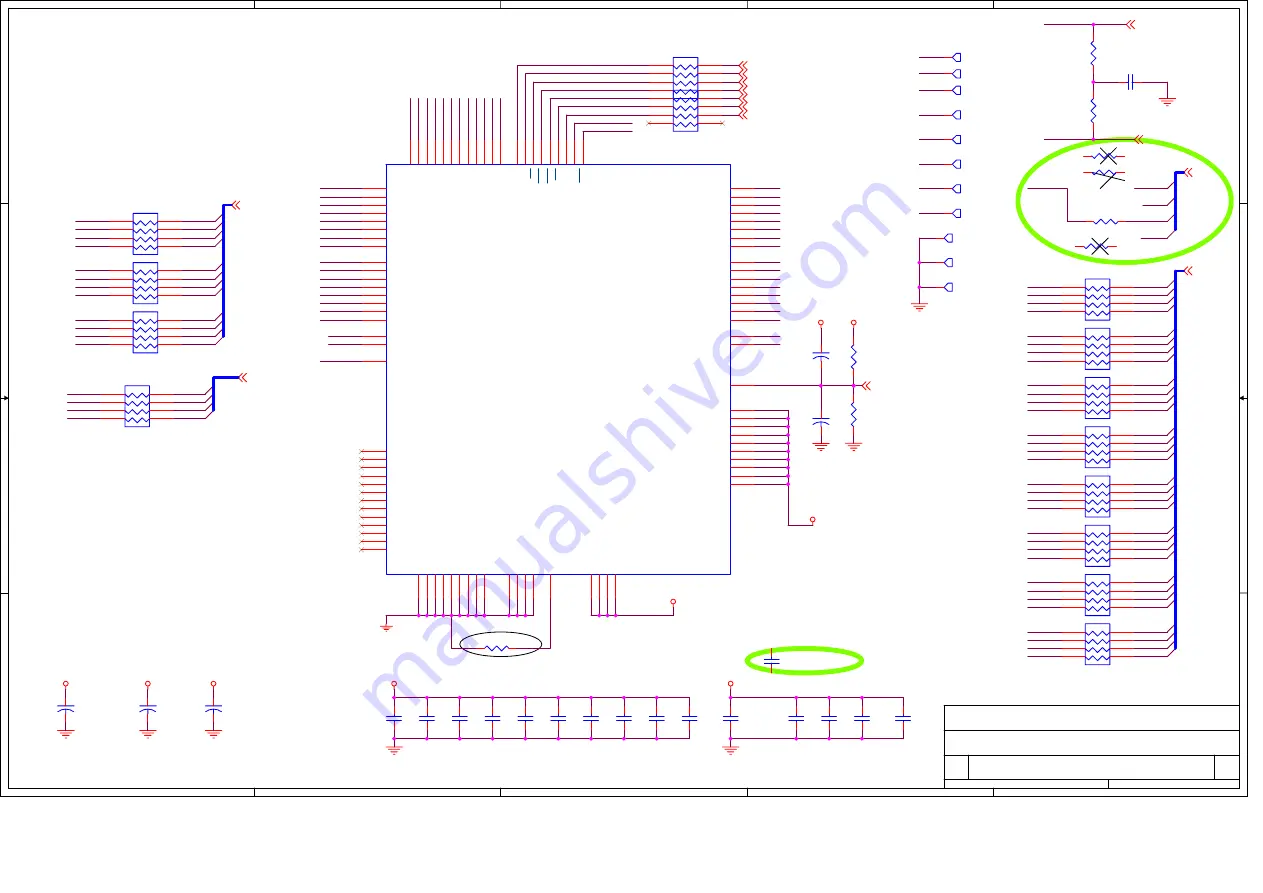

SDRAM DECOUPLING CAPACITORS

PRELIMINARY

Test pads for DDR

MEMORY DECOUPLING SCHEME

DDR_B2

DDR VDDMQ / VDDM de-caps

Each MD trace must be equal length.

Each DQS trace must be equal

length.

C90 MOVE PAGE 15.

R58 MOVED TO PAGE 5.

30TR04A LCD TV_MAIN

A-01

DDR

Qingdao Haier Electronics Co.,Ltd.

B

12

30

Tuesday, July 12, 2005

Title

Size

Document Number

Rev

Date:

Sheet

of

DQ20

DQ19

DQ22

DQ21

DQ16

DQ23

DQ17

DQ18

DQ6

DQ3

DQ4

DQ7

DQ5

DQ1

DQ0

DQ2

DQ30

DQ28

DQ31

DQ29

DQ26

DQ27

DQ25

DQ24

DQ14

DQ15

DQ13

DQ10

DQ9

DQ8

DQ11

MD25

MD22

MD11

MD9

MD31

MD23

DQ12

MD29

MD12

MD5

MD20

MD8

MD4

MD27

MD24

MD15

MD13

MD18

MD16

MD1

MD7

MD28

MD6

MD21

MD10

MD26

MD2

MD19

MD17

MD3

MD0

MD14

MD30

DDQS

DQS2

DQS3

DQS0

DQS1

CS0#

DQM0

MCLK0

RAS#

DDQS

CAS#

DQ23

MCLK0

MA

6

-

DQ9

DQ25

DQ26

MCLK0#

MCLK0

DQM3-

DQ8

DQ14

DQ27

DQ22

DQ21

DQ15

DQ3

M

A

11-

MA

2

-

DQ30

MA

0

-

MA

3

-

MA

9

-

DQ11

MCLK0#

MA

4

-

DQM0-

DQM1-

DQ10

DQ13

DQ28

DQ31

DQM2-

MA

5

-

MA

7

-

MVREF

MA

1

-

MA

8

-

DQ17

DQ24

DQ18

DQ12

M

A

10-

DQ29

DQ2

DDQS

DQ0

DQ1

DQ4

DQ5

DQ6

DQ7

DQ16

DQ19

DQ20

DQ23

CAS#-

MA0-

CLKE-

RAS#-

MA7-

MA3-

CS0#-

BA0-

MA2-

MA1-

MA5-

BA1-

WE#-

MA4-

MA6-

DQM2-

DQM0-

DQM3-

DQM1-

DQM3

DQM0

DQM1

DQM2

MA2

MA8

MA8-

MA11-

MA9-

MA6

MA4

MA9

MA1

MA0

MA10-

MA10

MA11

MA7

MA5

MA3

MCLK0#

MD[0..31]

DQS[0..3]

MCLK0#

MCLK0

CS0#

BA0

RAS#

DQM[0..3]

CAS#

WE#

BA1

MVREF

CLKE

MA[0..11]

VDDM

VDDMQ

VDDMQ

VDDMQ

VDDM

VDDMQ

VDDM

VDDMQ

VDDMQ

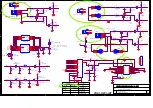

RP12 33Rx4

1

2

3

4

8

7

6

5

C83

100nF

C300

100nF

TP13

TP_T_C30

C82

100nF

C89

100nF

R282

0R

RP11 33Rx4

1

2

3

4

8

7

6

5

C80

100nF

TP11

TP_T_C30

R62

1K

C78

10uF/16V

RP37 33Rx4

1

2

3

4

8

7

6

5

R58

15R_DNS

C84

100nF

R59

15R_DNS

TP14

TP_T_C30

C88

100nF

R56

51R

C79

10uF/16V

C87

100nF

TP9

TP_T_C30

RP13 33Rx4

1

2

3

4

8

7

6

5

C299

100nF

R57

51R

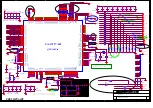

4M X 32 DDR

U3

TC59S6432CFT_4

53

55

28

26

27

25

23

56

24

57

31

32

33

34

47

48

49

50

51

45

36

29

30

94

54

87

88

90

43

2

8

14

22

59

67

73

58

15

35

65

97

98

100

1

3

4

6

7

60

61

63

64

68

69

71

72

9

10

12

13

17

18

20

21

74

75

77

78

80

81

83

84

5

11

62

52

70

76

16

46

66

79

96

95

86

99

92

82

19

85

38

39

40

89

41

42

44

91

37

93

CK

E

CL

K

CS

CA

S

RA

S

WE

DM0

DM1

DM2

DM3

A0

A1

A2

A3

A4

A5

A6

A7

A8/

AP

A9

A10

BA0

BA1

DQS

CL

K

NC

NC

NC

NC

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VDDQ

VREF

VD

D

VD

D

VD

D

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

VSSQ

VSSQ

VSSQ

MCL

VSSQ

VSSQ

VSS

VSS

VSS

VDDQ

VD

D

VDDQ

VDDQ

VSSQ

VSSQ

VSSQ

VSSQ

VSS

NC

NC

NC

NC

NC

NC

NC

DNC

A11

NC

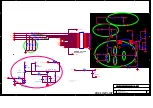

C301

100nF

C303

100nF

C75

100nF

C81

100nF

C90

100nF

TP8

TP_T_C30

C85

100nF

RP17 33Rx4

1

2

3

4

8

7

6

5

TP26

TP_T_C30

C76

100nF

TP16

TP_T_C30

RP38

33Rx4

1

2

3

4

8

7

6

5

RP14 33Rx4

1

2

3

4

8

7

6

5

RP36 33Rx4

1

2

3

4

8

7

6

5

RP10 33Rx4

1

2

3

4

8

7

6

5

C86

100nF

C77

10uF/16V

TP10

TP_T_C30

C74

100nF

RP39 33Rx4

1

2

3

4

8

7

6

5

R60

15R-->0R

R63

1K

RP15 33Rx4

1

2

3

4

8

7

6

5

TP12

TP_T_C30

C91

100nF

TP7

TP_T_C30

R61

15R_DNS

RP40

33Rx4

1

2

3

4

8

7

6

5

RP41 33Rx4

1

2

3

4

8

7

6

5

RP16 33Rx4

1

2

3

4

8

7

6

5

TP15

TP_T_C30

Summary of Contents for HLH26BB

Page 1: ...SERVICE MANUAL FOR LCD TV HLH26BB HLH32BB HLH37BB TV 8888 47 ...

Page 5: ...5 Connection sketch interpretation ...

Page 6: ......

Page 7: ...BLOCK DIAGRAM ...

Page 8: ......

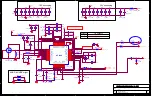

Page 9: ...6 Circuit diagram ...

Page 38: ...Sincere forever ...