MB95630H Series

368

FUJITSU SEMICONDUCTOR LIMITED

MN702-00009-1v0-E

CHAPTER 20 16-BIT RELOAD TIMER

20.6 Operations and Setting Procedure Example

Figure 20.6-10 Count Operation in Reload Mode (Event Count Mode)

●

Operation of one-shot mode

If the reload select bit (RELD) is "0", the value of the 16-bit counter halts at "0xFFFF" when

the 16-bit counter underflows ("0x0000"

→

"0xFFFF").

An interrupt request is output when the underflow request flag bit (UF) in the 16-bit reload

timer control status register (lower) (TMCSRLn) is set to "1" with the underflow interrupt

enable bit (INTE) set to "1".

The TOn pin outputs a square waveform indicating that counting is in progress. Figure 20.6-11

shows the count operation in one-shot mode.

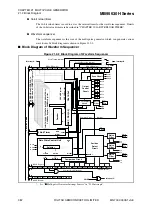

Figure 20.6-11 Counter Operation in One-shot Mode (Event Count Mode)

TIn pin

Co

u

nter

-1

0000

-1

0000

-1

0000

-1

D

a

t

a

lo

a

d

s

ign

a

l

UF

b

it

CNTE

b

it

TRG

b

it

TOn pin

Relo

a

d d

a

t

a

Relo

a

d d

a

t

a

Relo

a

d d

a

t

a

Relo

a

d d

a

t

a

TIn pin

Co

u

nter

-1

0000

-1

0000

D

a

t

a

lo

a

d

s

ign

a

l

UF

b

it

CNTE

b

it

TRG

b

it

TOn pin

Relo

a

d d

a

t

a

Relo

a

d d

a

t

a

FFFF

FFFF

W

a

it for

s

t

a

rt trigger inp

u

t