382

CHAPTER 20 UART2, UART3

20.7.1

Operation in Asynchronous Mode (Op. Modes 0 and 1)

When UART2, UART3 is used in operation mode 0 (normal mode) or operation mode 1

(multiprocessor mode), the asynchronous transfer mode is selected.

■

Operation in Asynchronous Mode

●

Transfer data format

Generally each data transfer in the asynchronous mode operation begins with the start bit ("L" level on bus)

and ends with at least one stop bit ("H" level). The direction of the bit stream (LSB first or MSB first) is

determined by the BDS bit of the Serial Status Register (SSR2/SSR3). The parity bit (if enabled) is always

placed between the last data bit and the (first) stop bit.

In operation mode 0 the length of the data frame can be 7 bits or 8 bits, with or without parity, and 1 or 2

stop bits.

In operation mode 1 the length of the data frame can be 7 bits or 8 bits with a following address-/data-

selection bit instead of a parity bit. 1 or 2 stop bits can be selected.

The calculation formula for the bit length of a transfer frame is:

Length = 1 + d + p + s

(d = number of data bits [7 or 8], p = parity [0 or 1], s = number of stop bits [1 or 2]

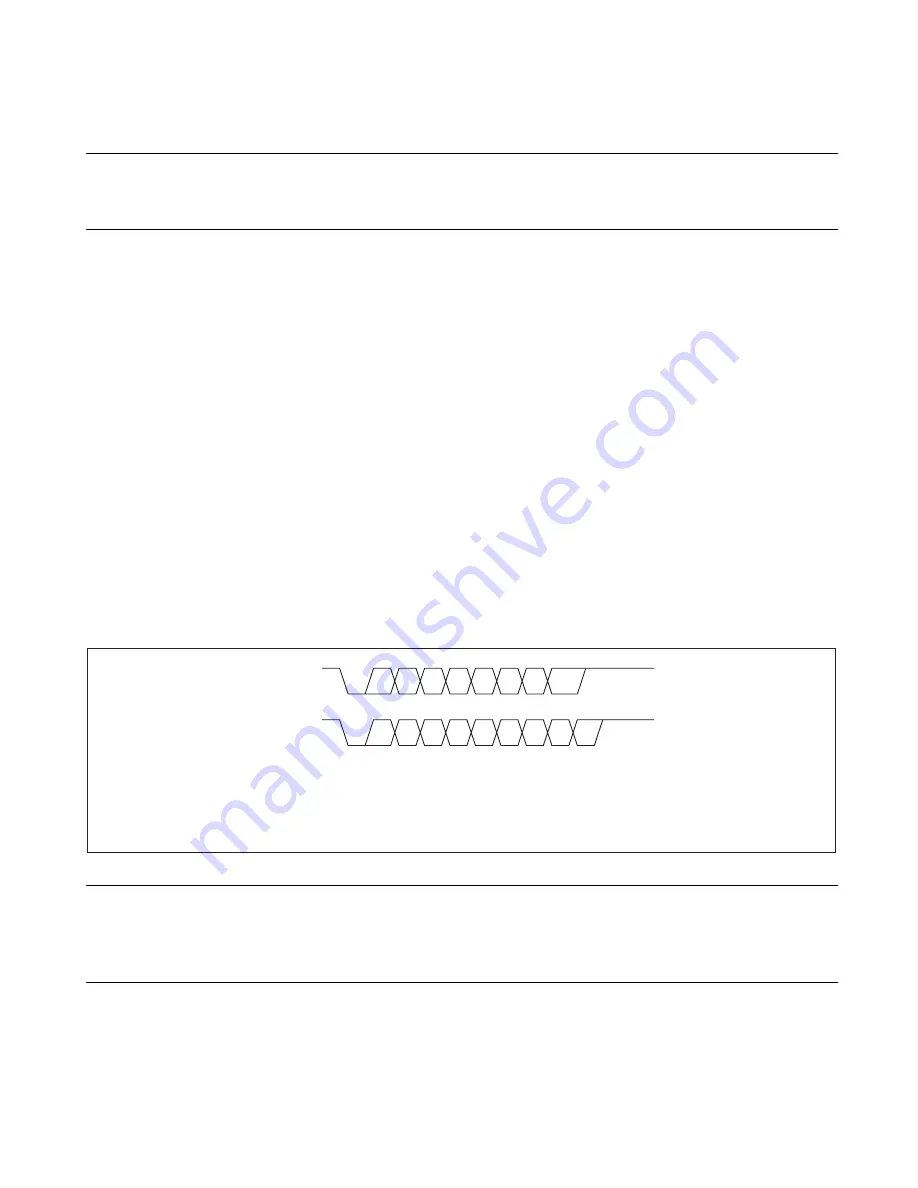

Figure 20.7-1 shows the data format in asynchronous mode.

Figure 20.7-1 Transfer Data Format (Operation Modes 0 and 1)

Note:

If BDS bit of the Serial Status Register (SSR2/SSR3) is set to "1" (MSB first), the bit stream

processes as: D7, D6, ..., D1, D0, (P).

During Reception both stop bits are detected, if selected. But the Reception data register full (RDRF) flag

will go "1" at the first stop bit. The bus idle flag (RBI of ECCR2/3) goes "1" after the second stop bit if no

further start bit is detected. (The second stop bit belongs to "bus activity", although it is just mark level.)

Operation mode 0

Operation mode 1

ST D0 D1 D2 D3 D4 D5 D6 D7/P SP SP

ST D0 D1 D2 D3 D4 D5 D6 D7 A/D SP

*1: D7 (bit 7) if parity is not provided and data length is 8 bits

P (parity) if parity is provided and data length is 7 bits

*2: only if SBL-bit of SCR3 is set to "1"

ST: Start bit SP: Stop bit A/D: Address/data selection bit in mode 1 (multiprocessor mode)

*1

*2

Summary of Contents for MB90390 Series

Page 2: ......

Page 4: ......

Page 17: ...xiii APPENDIX D List of Interrupt Vectors 690 INDEX 695 ...

Page 18: ...xiv ...

Page 132: ...104 CHAPTER 5 CLOCKS ...

Page 152: ...124 CHAPTER 6 CLOCK MODULATOR ...

Page 210: ...182 CHAPTER 11 TIME BASE TIMER ...

Page 218: ...190 CHAPTER 12 WATCHDOG TIMER ...

Page 264: ...236 CHAPTER 14 16 BIT RELOAD TIMER WITH EVENT COUNT FUNCTION ...

Page 274: ...246 CHAPTER 15 WATCH TIMER ...

Page 306: ...278 CHAPTER 17 DTP EXTERNAL INTERRUPTS ...

Page 338: ...310 CHAPTER 18 8 10 BIT A D CONVERTER ...

Page 364: ...336 CHAPTER 19 UART0 UART1 ...

Page 398: ...370 CHAPTER 20 UART2 UART3 Figure 20 5 2 ORE Set Timing Receive data RDRF ORE ...

Page 432: ...404 CHAPTER 20 UART2 UART3 ...

Page 482: ...454 CHAPTER 22 SERIAL I O ...

Page 560: ...532 CHAPTER 24 STEPPING MOTOR CONTROLLER ...

Page 582: ...554 CHAPTER 27 ROM MIRRORING MODULE ...

Page 632: ...604 CHAPTER 29 EXAMPLES OF SERIAL PROGRAMMING CONNECTION ...

Page 722: ...694 APPENDIX ...

Page 723: ...695 INDEX The index follows on the next page This is listed in alphabetic order ...

Page 740: ......