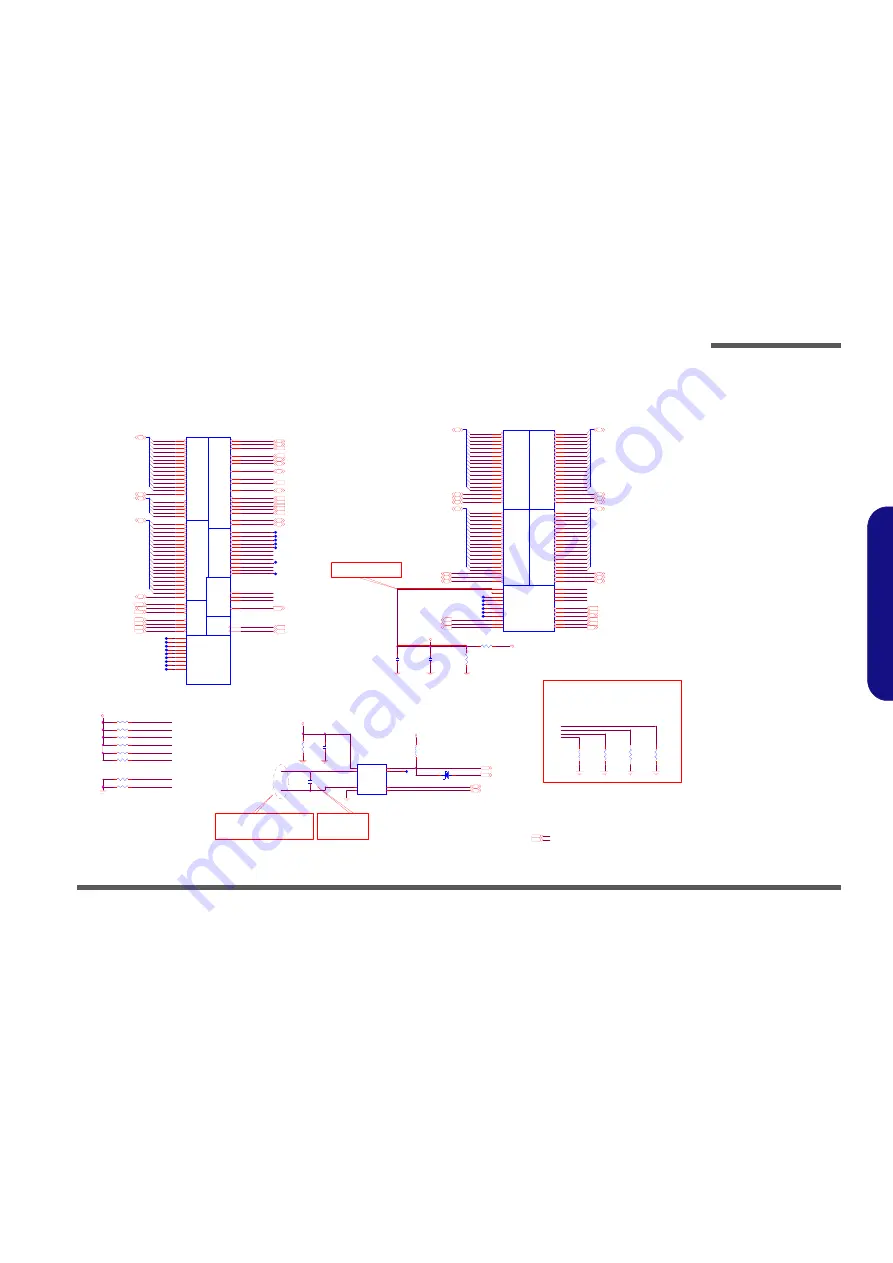

Schematic Diagrams

Intel Penryn 1/2 B - 3

B.Sch

e

m

a

tic D

iag

rams

Intel Penryn 1/2

Sheet 2 of 37

Intel Penryn 1/2

1. 05VS

3.3V

1. 05VS

C PU _GTLREF

3.3V

H_PWR GD 12

H_REQ#[4: 0]

4

H_BREQ# 4

H _I NTR

12

H_DSTBN#0

4

H_DBSY# 4

H_D STBP# 1

4

H_D#[ 63:0] 4

H_D #[63: 0]

4

CPU_BSEL2

4,17

H_I GN NE#

12

CLK_C PU_BCL K# 17

H_ AD STB#0

4

SMD _CPU_TH ER M 22

H_RS# 2

4

H _SMI #

12

CPU_BSEL0

4,17

H_DR DY# 4

H_I NIT#

12

H_C PU SLP# 4

3. 3V

12,13 ,1 4,15, 16, 18, 19,23 ,2 4,27, 28

CPU_BSEL1

4,17

H_DI NV#3 4

1.05VS

3,4,5, 7, 8,12,15, 17, 27

H_A#[35:3]

4

H_BNR # 4

H_D STBN#1

4

H_DI NV#2 4

H_A#[35:3]

4

CLK_C PU_BCL K 1 7

H_RS# 1

4

H _NMI

12

H_CPU RST# 4

H_ STPCLK#

12

H_DEFER# 4

PM_TH RMTRIP# 5,12,26

H_ADS#

4

PSI #

2 9

H _DI NV#1

4

H_D PW R# 4

H_D INV#0

4

H_HI TM# 4

H_A20M#

12

SMC _CPU_TH ER M 22

H_DSTBP#2 4

H_D#[ 63:0] 4

H_D PSL P# 12

H_ AD STB#1

4

H_FERR #

12

H_HI T#

4

H_D #[63: 0]

4

H_DSTBN#2 4

H_TRDY# 4

H_BPRI # 4

H_LOCK# 4

H_DSTBN#3 4

H_RS# 0

4

H_D STBP#0

4

H_D PR STP# 5, 12,29

H_DSTBP#3 4

PM_TH RM# 14

THERM_ALERT# 22

H_THERMDC

H_D#37

H_A#34

H_A#5

H_D#60

H _TC K

H _D#29

H _D#18

H_A#31

H_A#17

COMP0

H_D#33

H_D#49

H_D#42

COMP3

H _TD I

H_A#24

H _D#22

H _TR ST#

H_D#54

H_A#21

H_A#33

H _D#30

CPU_BSEL0

H _D#14

C OMP0

H_D#43

H _TDI

H _D#4

H _PREQ#

H_REQ#3

H _D#23

H _D#13

H _D#28

H _D#27

H _TMS

H_D#34

H _PRO CHOT#

H _PRO CHO T#

H_A#32

H _D#21

H _D#12

H _CPU RST#

H_D#32

H_REQ#1

H_A#12

H_A#8

H_THERMDA

H_D#45

COMP1

H _CPU RST#

H _D#26

H_A#13

H _I ER R#

H_A#26

H _TCK

H_A#27

H _D#3

H _D#20

H_D#39

H_A#9

H_D#47

H_A#30

COMP2

H _D#9

H_D#63

H_D#53

H_REQ#2

H_A#7

H_A#4

H _D#19

H_D#44

H_D#51

H_A#19

H _D#7

H_D#55

H _D#24

H _D#2

H_D#50

H_D#48

H_D#46

CPU_BSEL2

H_A#6

H_D#52

CPU_BSEL1

H _D#10

H_D#62

H _TRST#

H_A#15

H_A#23

H_A#22

H _IER R#

H _D#1

H_D#61

H_A#29

H _D#6

H _D#5

H_D#35

H _D#15

C OMP1

H _D#17

H_A#16

H_D#58

H _D#11

H_A#25

H_D#38

H_REQ#4

H_A#35

H _THERMD A

H_D#59

H _TMS

H_A#18

C OMP3

H _D#8

H_REQ#0

H_D#56

H_A#20

C OMP2

H_A#28

H _D#25

H _D#31

H_D#41

H_A#3

H_A#14

H_D#40

H _PREQ#

H _D#16

H_D#36

H _THERMD C

H _D#0

H_D#57

H_A#10

H_A#11

R23

54.9_1%_04

D 23

ASD 75 1V

A

C

R227

*10 0K_04

R21

27.4_1%_04

C 374

1U_6.3V_04

R209

649_1%_04

C330

0.0 1U _16V_X7R_04

R211

1K_1%_ 04

R226

*51_1%_04

R22 9

10K_04

R206

54.9_1%_0 4

R208

54.9_1%_0 4

R225

54.9_1%_0 4

R212

2K_ 1%_04

DA

T

A

G

R

P

0

D

AT

A G

R

P

1

DA

T

A

G

R

P

2

DA

T

A

G

R

P

3

M IS C

U15B

MOLEX_4743 0-6515

R 26

U 26

AA1

Y 1

E22

F24

J 24

J 23

H 22

F26

K22

H 23

N 22

K25

P26

R 23

E26

L23

M24

L22

M23

P25

P23

P22

T24

R 24

L25

G 22

T25

N 25

Y 22

AB24

V24

V26

V23

T22

U 25

U 23

F23

Y 25

W2 2

Y 23

W2 4

W2 5

AA23

AA24

AB25

AE24

AD24

G 25

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

E25

AC22

AD23

AF22

AC23

E23

K24

G 24

AF1

H 25

N 24

U 22

AC20

E5

B5

D 24

J 26

L26

Y 26

AE25

H 26

M26

AA26

AF24

AD 26

AE6

D 6

D 7

C 24

B22

B23

C 21

D 25

AF26

A26

C 23

C3

COMP[ 0]

COMP[ 1]

COMP[ 2]

COMP[ 3]

D[ 0] #

D[ 1] #

D[ 10] #

D[ 11] #

D[ 12] #

D[ 13] #

D[ 14] #

D[ 15] #

D[ 16] #

D[ 17] #

D[ 18] #

D[ 19] #

D[ 2] #

D[ 20] #

D[ 21] #

D[ 22] #

D[ 23] #

D[ 24] #

D[ 25] #

D[ 26] #

D[ 27] #

D[ 28] #

D[ 29] #

D[ 3] #

D[ 30] #

D[ 31] #

D [32]#

D [33]#

D [34]#

D [35]#

D [36]#

D [37]#

D [38]#

D [39]#

D[ 4] #

D [40]#

D [41]#

D [42]#

D [43]#

D [44]#

D [45]#

D [46]#

D [47]#

D [48]#

D [49]#

D[ 5] #

D [50]#

D [51]#

D [52]#

D [53]#

D [54]#

D [55]#

D [56]#

D [57]#

D [58]#

D [59]#

D[ 6] #

D [60]#

D [61]#

D [62]#

D [63]#

D[ 7] #

D[ 8] #

D[ 9] #

TEST5

DI NV[0]#

DI NV[1]#

DI NV[2]#

DI NV[3]#

DPRSTP#

DPSLP#

D PWR#

DSTBN [0] #

DSTBN [1] #

D STBN[2]#

D STBN[3]#

DSTBP[ 0]#

DSTBP[ 1]#

DSTBP[2]#

DSTBP[3]#

GTLREF

PSI#

PWRG OOD

SLP#

TEST3

BSEL[0]

BSEL[1]

BSEL[2]

TEST2

TEST4

TEST6

TEST1

TEST7

R228

56_04

C 369

1 000P_50V_X7R_04

C336

*1U _6. 3V_X5R_ 06

AD

DR

GR

OU

P

_

0

AD

DR

GR

O

U

P

_

1

CO

N

T

R

O

L

X

D

P

/IT

P

S

I

G

N

A

L

S

H CL K

TH ERM AL

RE

S

E

RV

E

D

IC

H

U15 A

MOLEX_47430-651 5

N3

P5

P2

L2

P4

P1

R1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

J4

U2

V4

M4

N5

T2

V3

B2

D2

D 22

L5

L4

K5

M3

N2

J1

A6

H1

M1

V1

D3

A22

A21

E2

AD4

AD3

AD1

AC4

G5

F1

C20

E1

H5

F21

A5

G6

E4

D20

C4

B3

C6

B4

H4

AC2

AC1

D21

K3

H2

K2

J3

L1

C1

F3

F4

G3

A3

D5

AC5

AA6

AB3

C7

A24

B25

AB5

G2

AB6

W3

AA4

AB2

AA3

F6

A[10] #

A[11] #

A[12] #

A[13] #

A[14] #

A[15] #

A[16] #

A[17] #

A[18] #

A[19] #

A[20] #

A[21] #

A[22] #

A[23] #

A[24] #

A[25] #

A[26] #

A[27] #

A[28] #

A[29] #

A[3]#

A[30] #

A[31] #

RSVD[ 01]

RSVD[ 02]

RSVD[ 03]

RSVD[ 04]

RSVD[ 05]

RSVD[ 06]

RSVD[ 07]

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A20M#

ADS#

ADSTB[ 0] #

ADSTB[ 1] #

RSVD[ 08]

BC LK[0 ]

BC LK[1 ]

BNR #

BPM[0] #

BPM[1] #

BPM[2] #

BPM[3] #

BPRI #

BR0#

D BR #

D BSY #

DEFER #

DRDY #

FERR#

HIT#

H ITM#

IERR #

I GNNE#

I NIT#

LI NT0

LI NT1

LO CK#

PRDY #

PR EQ #

PROC HOT#

REQ [0] #

REQ [1] #

REQ [2] #

REQ [3] #

REQ [4] #

RESET#

R S[0] #

R S[1] #

R S[2] #

SMI #

STPCL K#

TCK

TD I

TDO

THER MTR IP#

TH ER MDA

THERMDC

TMS

TRDY #

TR ST#

A[32] #

A[33] #

A[34] #

A[35] #

RSVD[ 09]

R205

54.9_1%_0 4

R207

54.9_1%_0 4

U 16

W 83L771AWG

1

2

3

4

5

6

7

8

VD D

D+

D-

THERM

GND

ALERT

SD ATA

SC LK

R 214

27.4_1%_ 04

R213

54.9_1%_04

0.5" max, Zo= 55 Ohms

? ADT7421 Colay

Near to Thermal

IC

COMP0, COMP2: 0.5" Max, Zo=27.4 Ohms

COMP1, COMP3: 0.5" Max, Zo=55 Ohms

Best estimate is 18 mils wide trace for outer

layers and 14 mils wide trace if on internal

layers.

CPU ONLY SUPPORT TO 35W

CPU_GRFE=0.7V

Layout note:

Layout Note:

Layout Note:

Route H_THERMDA and

H_THERMDC on same layer.

10 mil trace on 10 mil spacing.

Layout Note:

All manuals and user guides at all-guides.com