ESMT

F25L04PA

(2D)

Elite Semiconductor Memory Technology Inc.

Publication D

ate: Aug.

2012

Revision:

1.4

3/33

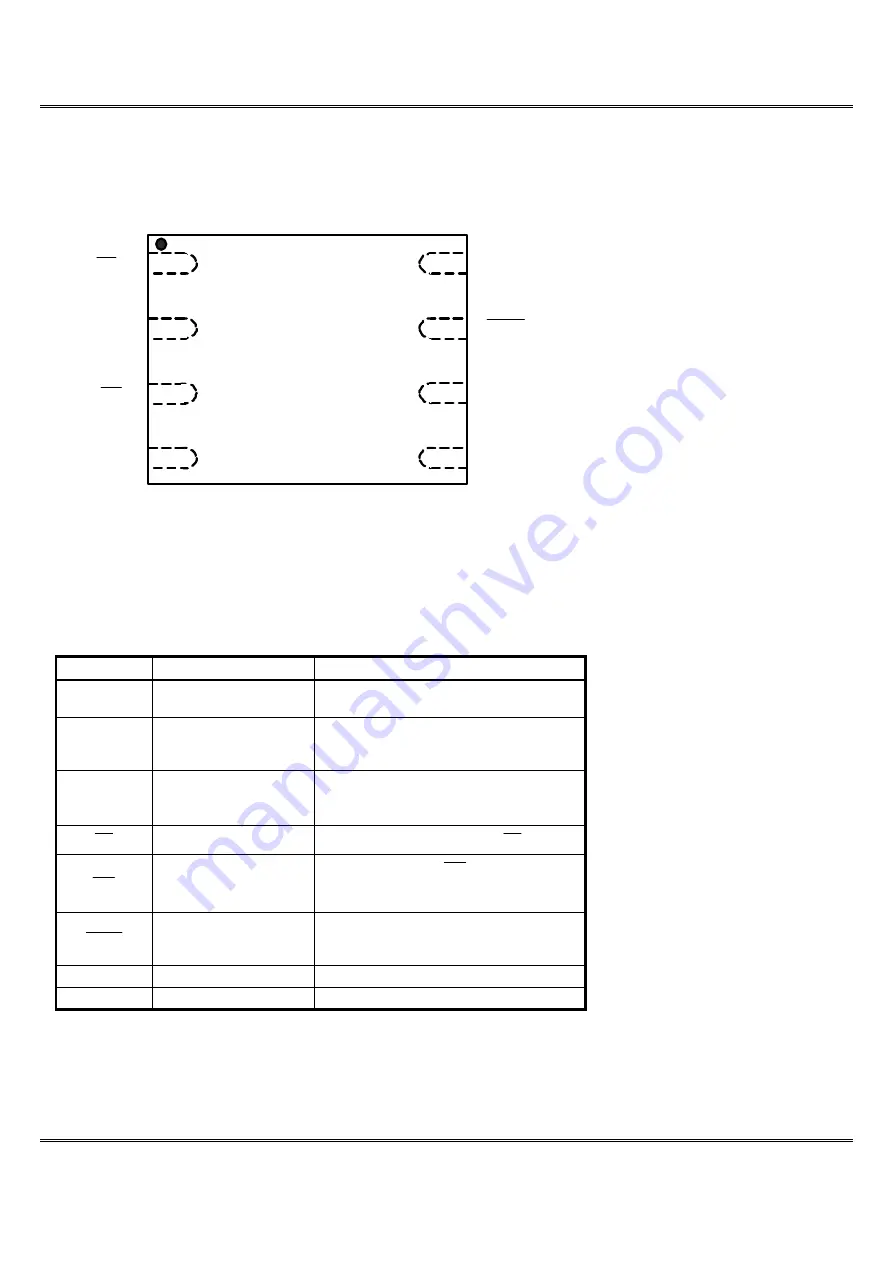

8- Contact WSON

(WSON 8C, 6mmX5mm Body, 1.27mm Contact Pitch)

PIN DESCRIPTION

Symbol Pin

Name

Functions

SCK Serial

Clock

To provide the timing for serial input and

output operations

SI

Serial Data Input

To transfer commands, addresses or data

serially into the device.

Data is latched on the rising edge of SCK.

SO

Serial Data Output

To transfer data serially out of the device.

Data is shifted out on the falling edge of

SCK.

CE

Chip Enable

To activate the device when CE is low.

WP

Write Protect

The Write Protect ( WP ) pin is used to

enable/disable BPL bit in the status

register.

HOLD

Hold

To temporality stop serial communication

with SPI flash memory without resetting

the device.

VDD

Power Supply

To provide power.

VSS Ground

1

2

3

4

8

7

6

5

CE

SO

WP

VSS

VDD

HOLD

SCK

SI