114

RTC Timer (Apollolake) - User Guide

Appendix

IND100077-195

DOC207017- rev 01 – 2018-09-24 - Created by: 6644

Page 6 of 12

Hatteland Display AS, Stokkastrandvegen 87B, N-5578 Nedre Vats, Norway

Tel: (+47) 4814 2200 - [email protected] - www.hatteland-display.com

User Guide RTC Timer - ApolloLake

All intellectual properties belongs to Hatteland Display AS

However, when the system is shutdown or restart, the BIOS firmware has no chance to do the time

copy, then the time of external RTC timer is not up-to-date.

In this case, we need an additional method to update RTC timer under OS, together with PCH time.

So RTC time will always be up-to-date.

This document will introduce the method of accessing RTC timer under OS.

2

Access RTC time

2.1

General Usage

2.1.1

SMBUS Access

The RTC timer is connected to SMBUS interface of processor PCH SMBUS controller. SMBUS I/O

registers are exposed in system IO space. The user can control the I/O register to conduct SMBUS

communication. The SMBUS Base Address is

0xF040

on ApolloLake S/L Board.

To operate read/write operations on SMBUS, the user has to follow the following procedure of writing

data into specific registers.

1.

Clear Host Status: Write data 0xFE to offset 0x00, wait the offset 0x00 value changing to

0x40.

2.

Set Device address: Write data of address (for RTC timer 0x64(write)/0x65(read)) to offset

0x04

3.

Set Slave Device Register Address: Write data of register index on target device to offset 0x03

4.

Set Slave Device Register Data (only required for write operation): Write data of register data

on target device to offset 0x05

5.

Set Execute bit: Write 0x48 to offset 0x02, and wait for offset 0x02 value change back to

0x08.

6.

For read operation, the readout data is available at offset 0x05.

2.1.2

Read Data from RTC timer

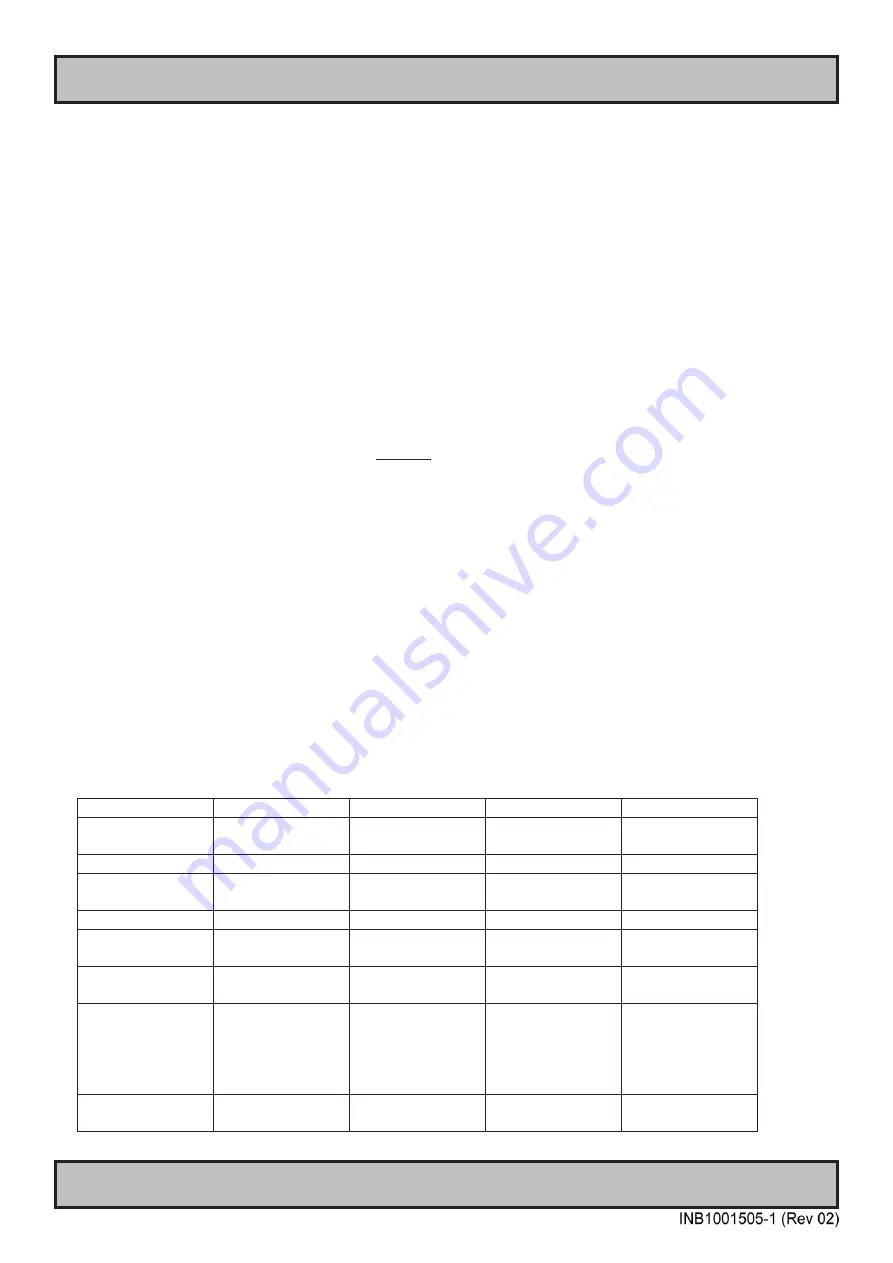

Step

Description

IN/OUT

Address

Data

1

Clear Host Status OUT

Base A

0x00

0xFE

2

Wait 1 sec

3

Read Host Status IN

Base A

0x00

4

Wait 1 sec

5

Read Host Status IN

Base A

0x00

(Expect 0x40)

6

Set Device

address

OUT

Base A

0x04

0x65

7

Set Slave Device

Register Address

OUT

Base A

0x03

0xXX

(See note 1

Time/Date

Register

Definition)

8

Set Execute Bit

OUT

Base A

0x02

0x48

Summary of Contents for Hatteland E Series

Page 8: ...8 This page left intentionally blank...

Page 9: ...9 General...

Page 17: ...17 Installation...

Page 41: ...41 Operation...

Page 44: ...44 This page left intentionally blank...

Page 45: ...45 Specifications...

Page 61: ...61 Specifications Accessories...

Page 65: ...65 Technical Drawings...

Page 70: ...70 This page left intentionally blank...

Page 71: ...71 Technical Drawings Accessories...

Page 88: ...88 This page left intentionally blank...

Page 89: ...89 Appendixes...

Page 134: ...134 Appendix IND100077 24 User Notes...

Page 136: ...Hatteland Technology AS www hattelandtechnology com Enterprise no NO974533146...