DLP-USB245M User Manual

Copyright © DLP Design 2002 Page 7 of 15

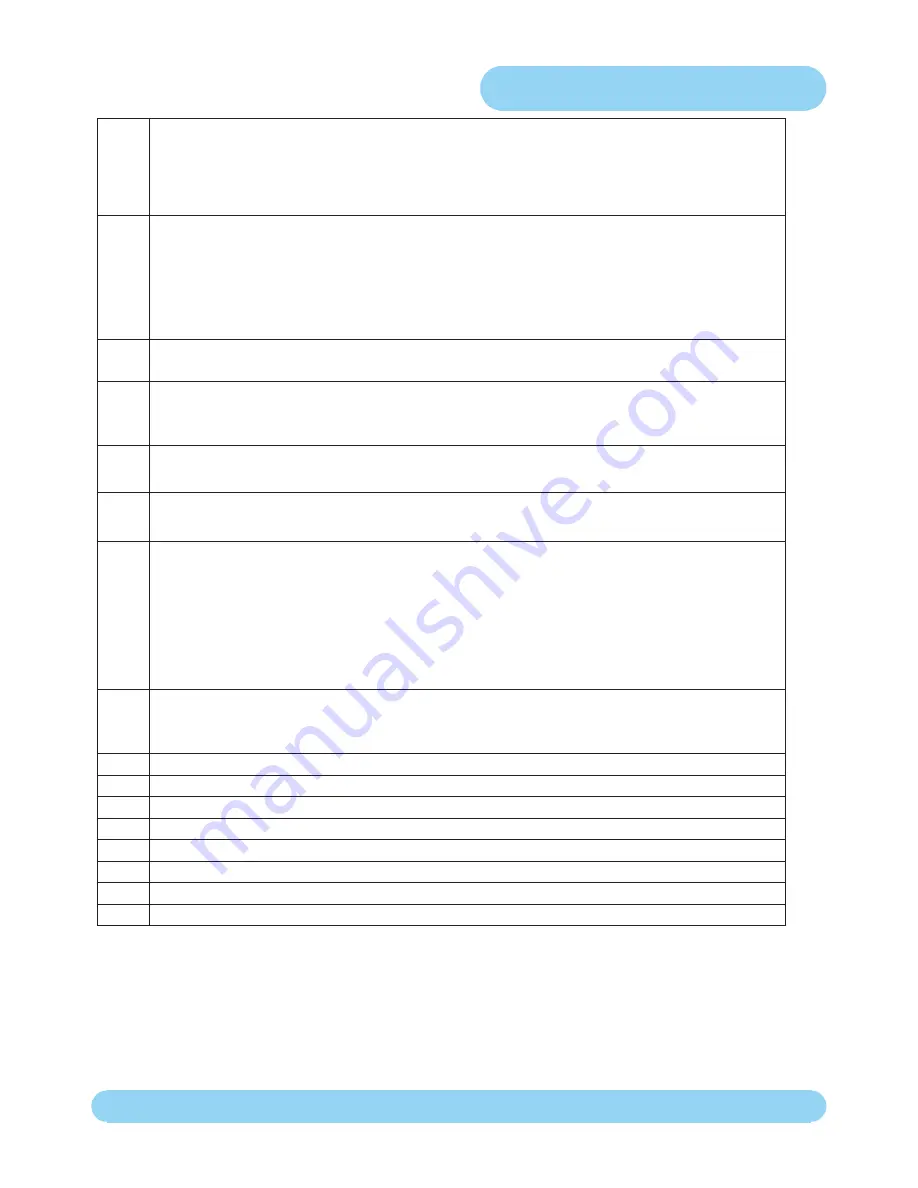

9

SND/WUP

(In) If the DLP-USB245M is in USB suspend, a positive edge on this pin (WAKEUP)

initiates a remote wakeup sequence. If the device is active (not in suspend) a positive edge on this

pin (SEND) causes the data in the write buffer to be sent to the PC on the next USB Data-In request

regardless of how many bytes are in the buffer.

10

VCC-IO

(In) 3.0 volt to +5.25 volt VCC to the UART interface pins 10..12, 14..16 and 18..25.

When interfacing with 3.3v external logic connect VCC-IO to the 3.3v supply of the external logic,

otherwise connect to VCC to drive out at 5v CMOS level. This pin must be connected to VCC from

the target electronics or EXTVCC.

11

EXTVCC

– (In) Use for applying main power (4.4 to 5.25 Volts) to the module. Connect to

PORTVCC if module is to be powered by the USB port (typical configuration)

12

PORTVCC

- (Out) Power from USB port. Connect to EXTVCC if module is to be powered by the

USB port (typical configuration). 500mA maximum current available to USB adapter and target

electronics if USB device is configured for high power.

13

RXF#

-

(Out) When low, at least 1 byte is present in the FIFO’s 128-byte receive buffer and is ready

to be read with RD#. RXF# goes high when the receive buffer is empty.

14

TXE#

-

When high, the FIFO’s 385 byte transmit buffer is full, or busy storing the last byte written.

Do not attempt to write data to the transmit buffer when TXE# is high.

15

WR

(In) When taken from a high to a low state, WR reads the 8 data lines and writes the byte into

the FIFO’s transmit buffer. Data written to the transmit buffer is sent to the host PC within the TX

buffer timeout value ( default 16mS ) and placed in the RS-232 buffer opened by the application

program. Note : The FT245BM allows the TX buffer timeout value to be reprogrammed to a value

between 1 and 255mS depending on the applicaton requirement, also the SND pin can be used to

send any remaining data in the TX buffer regardless of the timeout value.

16

RD#

(In) When pulled low, RD# takes the 8 data lines from a high impedance state to the current

byte in the FIFO’s receive buffer. Taking RD# high returns the data pins to a high impedance state

and prepares the next byte (if available) in the FIFO to be read.

17

D7

I/O Bi-directional Data Bus Bit # 7

18

D6

I/O Bi-directional Data Bus Bit # 6

19

D5

I/O Bi-directional Data Bus Bit # 5

20

D4

I/O Bi-directional Data Bus Bit # 4

21

D3

I/O Bi-directional Data Bus Bit # 3

22

D2

I/O Bi-directional Data Bus Bit # 2

23

D1

I/O Bi-directional Data Bus Bit # 1

24

D0

I/O Bi-directional Data Bus Bit # 0