DS1821

12 of 18

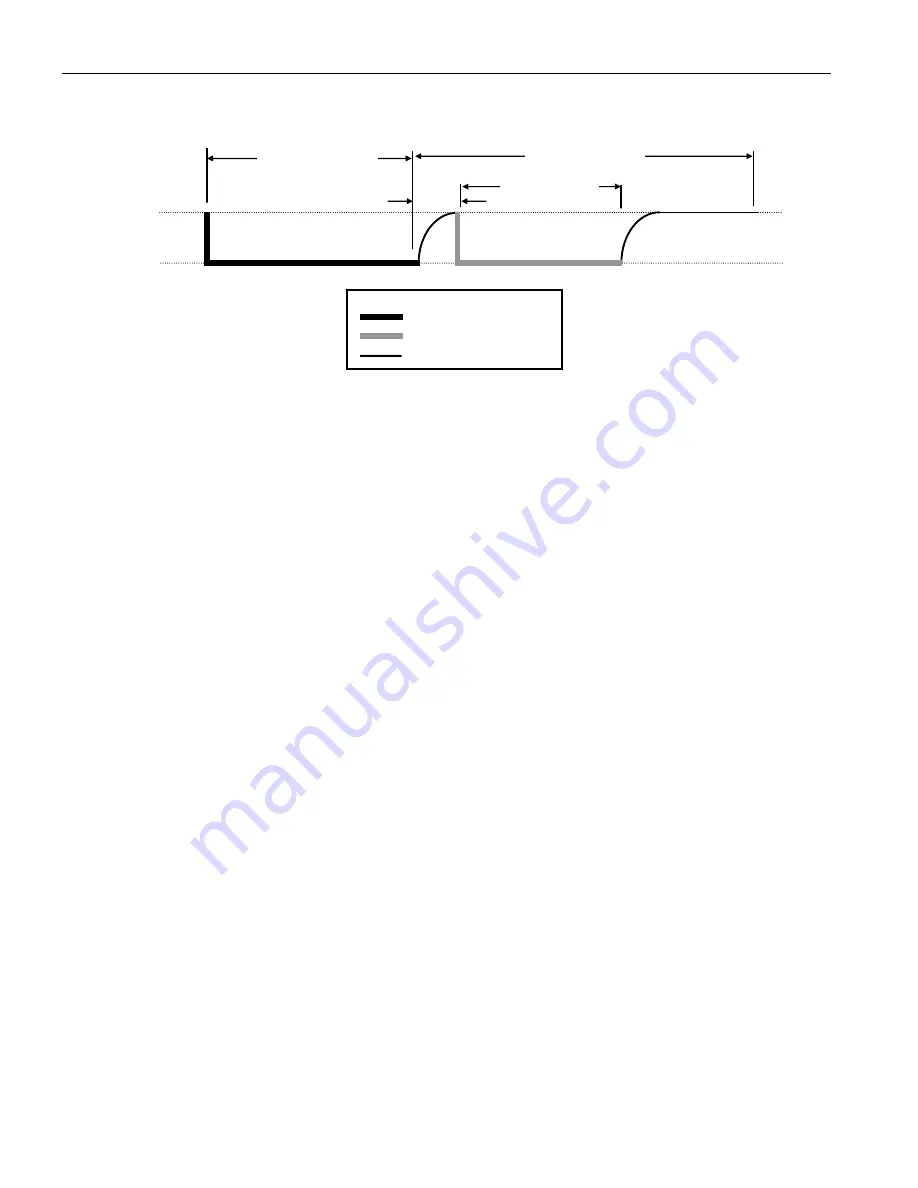

INITIALIZATION TIMING

Figure 7

READ/WRITE TIME SLOTS

The bus master writes data to the DS1821 during write time slots and reads data from the DS1821 during

read time slots. One bit of data is transmitted over the 1-Wire bus per time slot.

WRITE TIME SLOTS

There are two types of write time slots: “Write 1” time slots and “Write 0” time slots. The bus master

uses a Write 1 time slot to write a logic 1 to the DS1821 and a Write 0 time slot to write a logic 0 to the

DS1821. All write time slots must be a minimum of 60

μ

s in duration with a minimum of a 1

μ

s recovery

time between individual write slots. Both types of write time slots are initiated by the master pulling the

1-Wire bus low (see Figure 8).

To generate a Write 1 time slot, after pulling the 1-Wire bus low, the bus master must release the 1-Wire

bus within 15

μ

s. When the bus is released, the 5k pullup resistor will pull the bus high. To generate a

Write 0 time slot, after pulling the 1-Wire bus low, the bus master must continue to hold the bus low for

the duration of the time slot (at least 60

μ

s).

The DS1821 samples the 1-Wire bus during a window that lasts from 15

μ

s to 60

μ

s after the master

initiates the write time slot. If the bus is high during the sampling window, a 1 is written to the DS1821.

If the line is low, a 0 is written to the DS1821.

READ TIME SLOTS

The DS1821 can only transmit data to the master when the master issues read time slots. Therefore, the

master must generate read time slots immediately after issuing a read command (e.g., Read Temperature

[AAh]), so that the DS1821 can provide the requested data. All read time slots must be a minimum of 60

μ

s in duration with a minimum of a 1

μ

s recovery time between slots. A read time slot is initiated by the

master device pulling the 1-Wire bus low for a minimum of 1

μ

s and then releasing the bus (see Figure

8). After the master initiates the read time slot, the DS1821 will begin transmitting a 1 or 0 on the bus.

The DS1821 transmits a 1 by leaving the bus high and transmits a 0 by pulling the bus low. When

transmitting a 0, the DS1821 will release the bus by the end of the time slot, and the bus will be pulled

back to its high idle state by the pullup resister. Output data from the DS1821 is valid for 15

μ

s after the

falling edge that initiated the read time slot. Therefore, the master must release the bus and then sample

the bus state within 15

μ

s from the start of the slot.

LINE TYPE LEGEND

Bus master pulling low

DS1821 pulling low

Resistor pull-up

V

DD

GND

1-WIRE BUS

480

μ

s minimum

480

μ

s minimum

DS1821 T

X

presence pulse

60-240

μ

s

MASTER T

X

RESET PULSE

MASTER R

X

DS1821

waits 15-60

μ

s