PSoC CY8CTMG20x and CY8CTST200 TRM, Document No. 001-53603 Rev. *C

129

I2C Slave

Bit 3: Address.

This bit is set when an address is received. This consists of

a Start or Restart, and an address byte.

In slave mode when this status is set, firmware reads the

received address from the data register and compares it

with its own address. If the address does not match, the

firmware writes a NACK indication to this register. No further

interrupts occur until the next address is received. If the

address does match, firmware must ACK the received byte,

then byte complete interrupts are generated on subsequent

bytes of the transfer.

When in I

2

C compatibility mode the Address bit should not

be cleared between a start and the next byte complete. If it

is cleared during this time the start status is cleared inter-

nally.

Bit 2: Transmit.

This bit sets the direction of the shifter for

a subsequent byte transfer. The shifter is always shifting in

data from the I

2

C bus, but a write of ‘1’ enables the output of

the shifter to drive the SDA output line. Since a write to this

register initiates the next transfer, data must be written to the

data register before writing this bit. In receive mode, the pre-

viously received data must have been read from the data

register before this write. Firmware derives this direction

from the RW bit in the received slave address.

This direction control is only valid for data transfers. The

direction of address bytes is determined by the hardware.

Bit 1: LRB.

Last Received Bit. This is the last received bit

in response to a previously transmitted byte. In transmit

mode, the hardware sends a byte from the data register and

clock in an acknowledge bit from the receiver. Upon the sub-

sequent byte complete interrupt, firmware checks the value

of this bit. A ‘0’ is the ACK value and a ‘1’ is a NACK value.

The meaning of LRB depends upon the current operating

mode.

‘0‘: ACK.

The master wants to read another byte. The

slave loads the next byte into the

and sets

the Transmit bit in the I2C_SCR register to continue the

transfer.

‘1’: NACK.

The master is done reading bytes. The slave

reverts to IDLE state on the subsequent I2C_SCR write

(regardless of the value written).

Bit 0: Byte Complete.

The I

2

C hardware operates on a

byte basis. In transmit mode, this bit is set and an interrupt is

generated at the end of nine bits (the transmitted byte + the

received ACK). In receive mode, the bit is set after the eight

bits of data are received. When this bit is set, an interrupt is

generated at these data sampling points, which are associ-

ated with the SCL input clock rising (see details in

). If the PSoC device responds with a

write back to this register before the subsequent falling edge

of SCL (which is approximately one-half bit time), the trans-

fer continues without interruption. However, if the device

cannot respond within that time, the hardware holds the

SCL line low, stalling the I

2

C bus. A subsequent write to the

I2C_SCR register releases the stall.

For additional information, refer to the

15.3.11

I2C_DR Register

The I

2

C Data Register (I2C_DR) provides read/write access

to the Shift register.

Bits 7 to 0: Data[7:0].

This register is not buffered; there-

fore, writes and valid data reads occur at specific points in

the transfer. These cases are outlined as follows:

■

Slave Receiver

– Data in the I2C_DR register is only

valid for reading when the Byte Complete status bit is

set. Data bytes must be read from the I2C_DR register

before writing to the

, which continues

the transfer.

■

Slave Transmitter

– Data bytes must be written to the

I2C_DR register before the Transmit bit is set in the

, which continues the transfer.

For additional information, refer to the

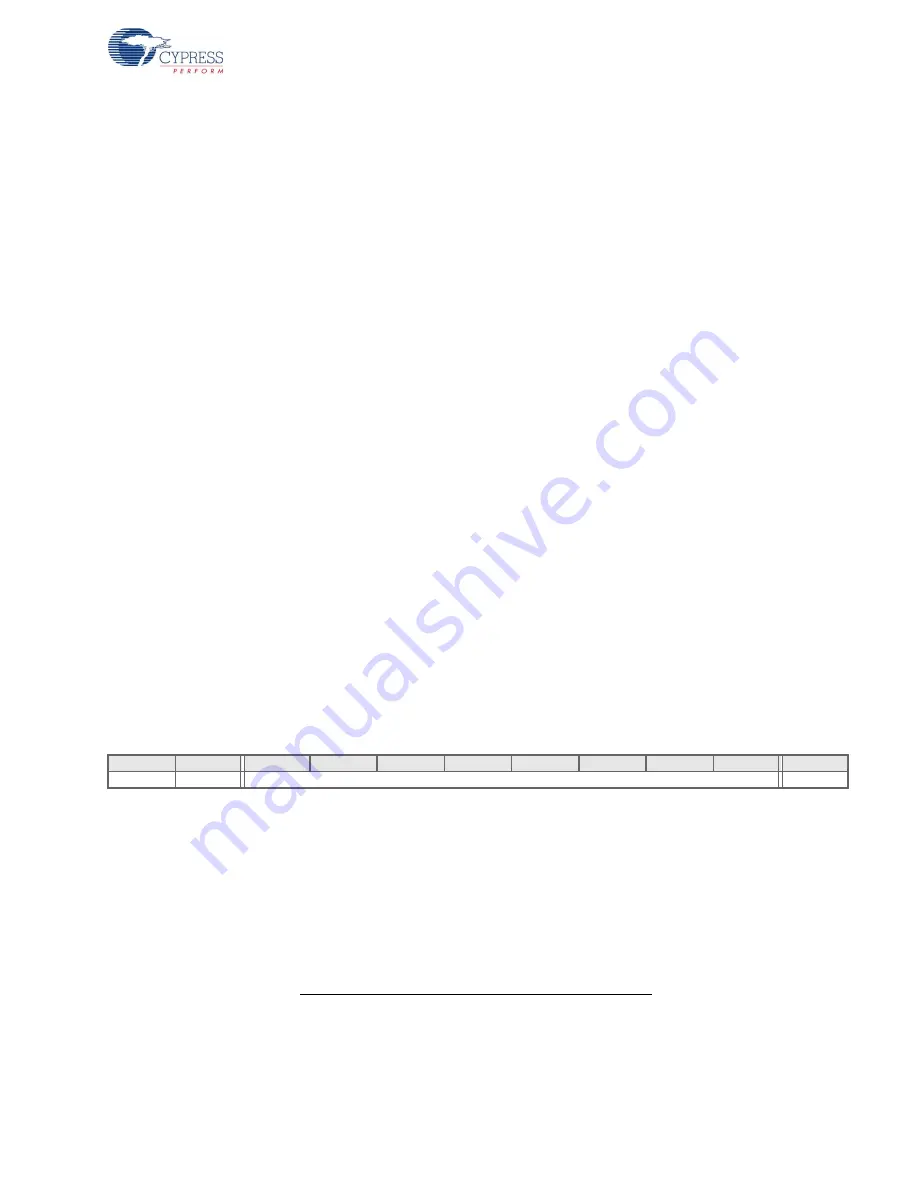

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Access

0,D8h

Data[7:0]

RW : 00

Summary of Contents for PSoC CY8CTMG20 Series

Page 4: ...4 Contents Overview Feedback...

Page 26: ...26 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Section B PSoC Core Feedback...

Page 82: ...82 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Sleep and Watchdog Feedback...

Page 134: ...134 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C I2C Slave Feedback...

Page 142: ...142 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C System Resets Feedback...

Page 160: ...160 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C SPI Feedback...

Page 182: ...182 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Full Speed USB Feedback...

Page 302: ...302 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Glossary Feedback...