240

PSoC CY8CTMG20x and CY8CTST200 TRM, Document No. 001-53603 Rev. *C

I2C_SCR

0,D7h

21.3.52 I2C_SCR

I

2

C Status and Control Register

This register is used by the slave to control the flow of data bytes and to keep track of the bus state during a transfer.

Bits in this register are held in reset until one of the enable bits in I2C_CFG is set. In the table above, note that the reserved

bit is a grayed table cell and not described in the bit description section below. Reserved bits must always be written with a

value of ‘0’. For additional information, refer to the

Register Definitions on page 122

in the I2C Slave chapter

.

7

Bus Error

0

Status bit. It must be cleared by firmware by writing a ‘0’ to the bit position. It is never

cleared by the hardware.

1

A misplaced Start or Stop condition was detected.

5

Stop Status

0

Status bit. It must be cleared by firmware with a write of ‘0’ to the bit position. It is never

cleared by the hardware.

1

A Stop condition was detected.

4

ACK

Acknowledge Out. Bit is automatically cleared by hardware upon a Byte Complete event.

0

NACK the last received byte.

1

ACK the last received byte

3

Address

0

Status bit. It must be cleared by firmware with a write of ‘0’ to the bit position.

1

The received byte is a slave address.

2

Transmit

Bit is set by firmware to define the direction of the byte transfer. Any Start detect or a write to the Start

or Restart generate bits when operating in master mode also clears the bit.

0

Receive mode.

1

Transmit mode.

1

LRB

Last Received Bit. The value of the 9

th

bit in a Transmit sequence, which is the acknowledge bit from

the receiver. Any Start detect or a write to the Start or Restart generate bits when operating in master

mode also clears the bit.

0

Last transmitted byte was ACK’ed by the receiver.

1

Last transmitted byte was NACK’ed by the receiver.

0

Byte Complete

Transmit/Receive Mode:

0

No completed transmit/receive since last cleared by firmware. Any Start detect or a write to

the Start or Restart generate bits when operating in master mode also clears the bit.

Transmit Mode:

1

Eight bits of data have been transmitted and an ACK or NACK has been received.

Receive Mode:

1

Eight bits of data have been received.

Individual Register Names and Addresses:

0,D7h

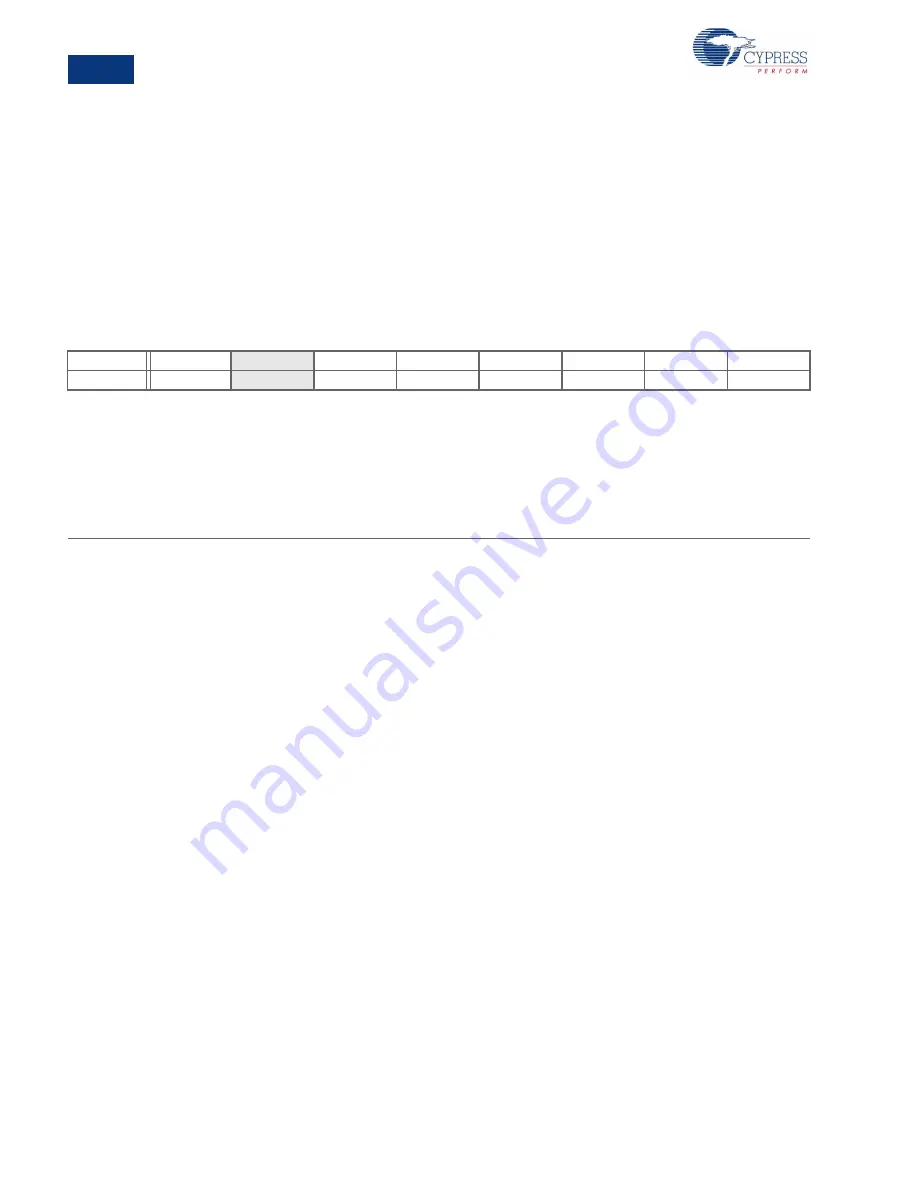

I2C_SCR : 0,D7h

7

6

5

4

3

2

1

0

Access : POR

RC : 0

RC : 0

RW : 0

RC : 0

RW : 0

RC : 0

RC : 0

Bit Name

Bus Error

Stop Status

ACK

Address

Transmit

LRB

Byte Complete

Bit

Name

Description

Summary of Contents for PSoC CY8CTMG20 Series

Page 4: ...4 Contents Overview Feedback...

Page 26: ...26 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Section B PSoC Core Feedback...

Page 82: ...82 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Sleep and Watchdog Feedback...

Page 134: ...134 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C I2C Slave Feedback...

Page 142: ...142 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C System Resets Feedback...

Page 160: ...160 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C SPI Feedback...

Page 182: ...182 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Full Speed USB Feedback...

Page 302: ...302 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Glossary Feedback...