6

.

Appendix

PT-955LX / LXF User’s manual

101

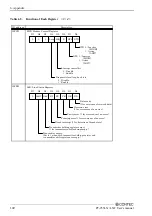

Table 6.5. Function of Each Register < 2 / 4 >

IIR : Interrupt Identification Register

D7

D6

D5

D4

D3

D2

D1

D0

Interrupt details

03FAH

I/O address

Description

LCR : Line Contror Regester

03FBH

1: Do not generate interrupts

0: Generate interrupts

0

0

0

0

0

bit2

0

bit1

0

bit0

1

Priority

Description

Interrupts are not generated.

Generated by overrun, parity, framing error or break

interrupt.

Cleared when the line status register is read.

Generated when the receive buffer register is ready.

Cleared when the receiving buffer is read.

Generated when the transmitter holding register is

empty. Cleared when the IIR is read or when

transmitted data is written to THR.

Modem status interrupt is generated.

(CTS, DSR, RI, CD)

Cleared when the modem status register is read.

1

1

0

1

0

0

0

1

0

0

0

0

1 (high)

2

3

4 (low)

D7

D6

D5

D4

D3

D2

D1

D0

0 : 1 STOP bit

1 : 1.5 STOP bits at 5-bit length

2 STOP bits at 6-, 7-, or 8-bit length

0 : Disable parity

1 : Enable parity

0 : Odd parity

1 : Even parity

0 : Disable stick parity

1 : Enable stick parity

0 : Break signal off

1 : Send break signal

DLAB (Divisor Latch Access Bit)

In order to access the divisor latch register, you need to set the bit

to 1. To access another register, set the bit to 0.

D1

0

0

1

1

D0

0

1

0

1

Bit table

5

6

7

8

Summary of Contents for PT-955LX-DC5000

Page 1: ...IPC Series PANEL PC 955 Series Fanless Atom N270 CF 12 1 model User s Manual CONTEC CO LTD...

Page 7: ...vi PT 955LX LXF User s manual...

Page 19: ...2 System Reference 12 PT 955LX LXF User s manual...

Page 29: ...3 Hardware Setup 22 PT 955LX LXF User s manual...

Page 39: ...4 Each Component Function 32 PT 955LX LXF User s manual...