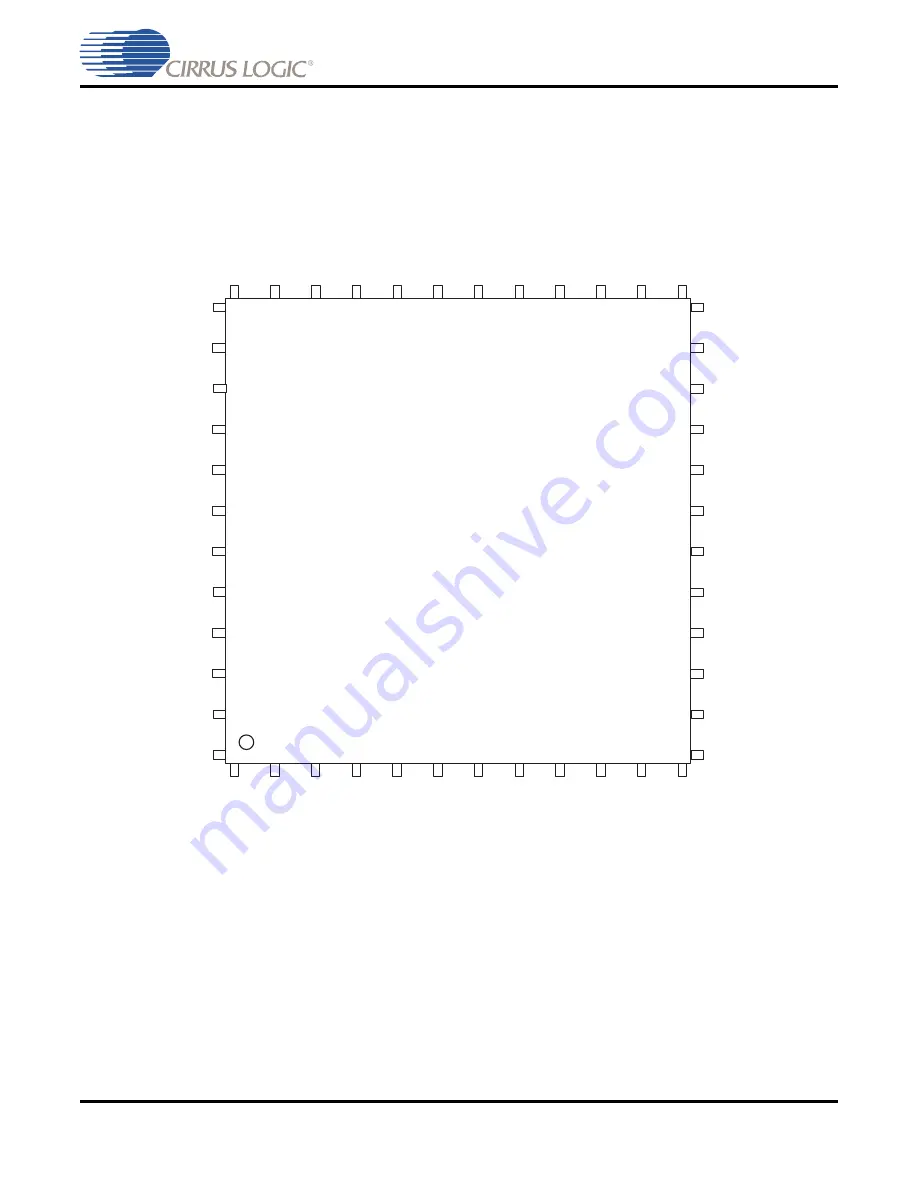

48-Pin LQFP Pin Assigments

CS485xx Hardware User’s Manual

DS734UM7

Copyright 2009 Cirrus Logic, Inc.

9-16

Figure 9-12

shows the 48-Pin LQFP Pin Layout of the CS48520.

Figure 9-12. 48-Pin LQFP Pin Layout of CS48520

XTO

XTI

GNDA

PLL_REF_RES

VDDA (3.3V)

GPIO1

GPIO2

GPIO

16,

DAI

1_DAT

A

0

GPIO0

38

40

41

42

43

45

46

GPIO13, SCP_BSY#, EE_CS#

GPOI12, SCP_IRQ#

GP

IO

10,

S

CP

__M

IS

O

/S

DA

GP

IO

9,

S

C

P

_M

O

S

I

GPI

O

11,

S

CP_CLK

35

33

31

30

28

26

25

GN

D

4

GNDIO4

VDD3

GND3

VDDIO3

G

NDIO

3

23

22

21

19

17

15

1

GPIO5,

XMTA

GPIO

3,

HS1

DAO1_DATA0, HS0

DAO_LRCLK

DAI1_

LRCLK

GPIO18,

D

AO_MCLK

DA

I1

_SCLK

VDD1

GND1

DAO_SCLK

GPIO4,

H

S2

RESET

#

VDDI

O1

GNDI

O1

G

P

IO6,

DAO2

_DATA

0,

H

S3

GPIO7,

HS4

VDD

2

GND2

VDDIO2

GNDIO2

2

3

4

5

6

7

9

10

11

12

GPIO8, SCP_CS#

TE

S

T

DBDA

DBCK

XTAL_OUT

GPIO15, DAI2_SCLK

GPIO14, DAI2_LRCLK

GPIO17, DAI2_DATA0

CS48520

48 LQFP

8

13

14

16

18

20

24

27

29

32

34

36

37

39

44

47

48