— 62 —

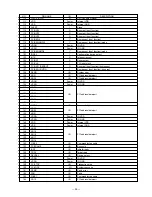

PIN NAME

I/O

DESCRIPTION

MA [9:0]

MD [63:0]

~WE

~RAS

~CAS

~CS0

~DQM

[7:0]

DSF

BA

SDCK

SDCKEN

~ROMEN

O

I/O

O

O

O

O

O

O

O

I/O

I/O

O

External Memory Address Bus. The video memory row and column addresses are multiplexed on these

lines.

External Memory Data Bus

External Memory Write Strobe

External Memory SDRAM Row Address Select

External SGRAM Column Address Select

External SGRAM Chip Select 0, select 1st 1MB within the 2MB memory, or select 1st 2MB within the 4MB

memory

External SGRAM I/O mask [7:0]. DQM [7:0] are byte specific. DQM0 masks MD [7:0], DQM1 masks MD [15:8],

…,and DQM7 masks MD [63:58].

External SGRAM Block write

External SGRAM Bank Select. SDRAM has dual internal banks. Bank address defines to which bank the

current command is being applied.

External SGRAM clock. SDCK is driven by the memory clock. All SDRAM input signals are sampled on the

positive edge of SDCK.

External SGRAM clock enable. SDCKEN activates (HIGH) and deactivates (LOW) the SDCLK signal.

Deactivating the SDCK provides POWER-DOWN and SELF-REFRESH mode.

ROM Enable

External Display Memory Interface

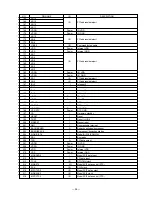

Flat Panel Interface

FDATA

[23:0]

LP/FHSYNC

FP/FVSYNC

M/

DE

FPSCLK

FPEN

FPVDDEN

VBIASEN

O

O

O

O

O

O

O

O

Flat Panel Data bit 23 to bit 0. Note: For SM712, the upper 12 bits [25:24] are multiplexed with ZV port, and

the upper 12 bits [23:11] are dedicated for flat panel data

DSTN LCD: Line Pulse

TFT LCD: LCD Horizontal Sync

DSTN LCD: Frame Pulse

TFT LCD: LCD vertical sync

M-signal or Display Enable. This signal is used to indicate the active horizontal display time.

FPR3E [7] is used to select

1 = M-signal

0 = Display Enable

Flat Panel Shift Clock. This is the pixel clock for Flat Panel Data.

Flat Panel Enable. This signal needs to become active after all panel voltages, clocks, and data are sup-

plied. This signal also needs to become inactive before any panel voltages or control signals are removed.

FPEN is part of the VESA FPDI-1B specification.

Flat Panel VDD Enable. This signal is used to control LCD logic power.

Flat Panel Voltage Bias Enable. This signal is used to control LCD Bias power.

Summary of Contents for QT-6100

Page 1: ...SERVICE MANUAL ELECTRONIC CASH REGISTER without price QT 6100 EX 819 AUG 2008 QT 6100 ...

Page 67: ... 65 8 11 ETHERNET CONTROLLER IC28 LAN91C113 8 11 1 Pin Assignment 8 11 2 Block Diagram ...

Page 92: ... 90 11 PCB LAYOUT MAIN PCB E819 1 PCB TOP VIEW ...

Page 93: ... 91 MAIN PCB E819 1 PCB BOTTOM VIEW ...

Page 94: ... 92 INTERFACE PCB E819 S1 PCB TOP VIEW BOTTOM VIEW LED PCB E820 LED PCB TOP VIEW BOTTOM VIEW ...

Page 108: ... 106 Model Name Board No Drawing No CASIO COMPUTER CO LTD QT 6100 EX 819 E820 LED LED ...

Page 120: ... 118 EXPLODED VIEW QT 6060D 2 11 17 14 15 20 Sales Option 16 5 6 12 13 18 19 8 7 10 3 1 4 9 5 ...

Page 135: ... 133 18 DRAWER DL 3616 ...

Page 137: ... 135 19 DRAWER DL 3617 ...