UM AX032200 Version 1.0 14-46

If the FMI used is anything other than one of those in Table 4, then both the low and the

high faults will be assigned the same FMI. This condition should be avoided, as the log

will still use different OC for the two types of faults, even though they will be reported

the same in the DTC.

It is the user’s responsibility to make sure this does not happen.

When the fault is linked to a DTC, a non-volatile log of the occurrence count (OC) is kept. As soon

as the controller detects a new (previously inactive) fault, it will start decrementing the

Delay

Before Sending DM1

timer for the Diagnostic function block. If the fault has remained present

during the delay time, then the controller will set the DTC to active, and it will increment the OC in

the log. A DM1 will immediately be generated that includes the new DTC. The timer is provided so

that intermittent faults do not overwhelm the network as the fault comes and goes, since a DM1

message would be sent every time the fault shows up or goes away.

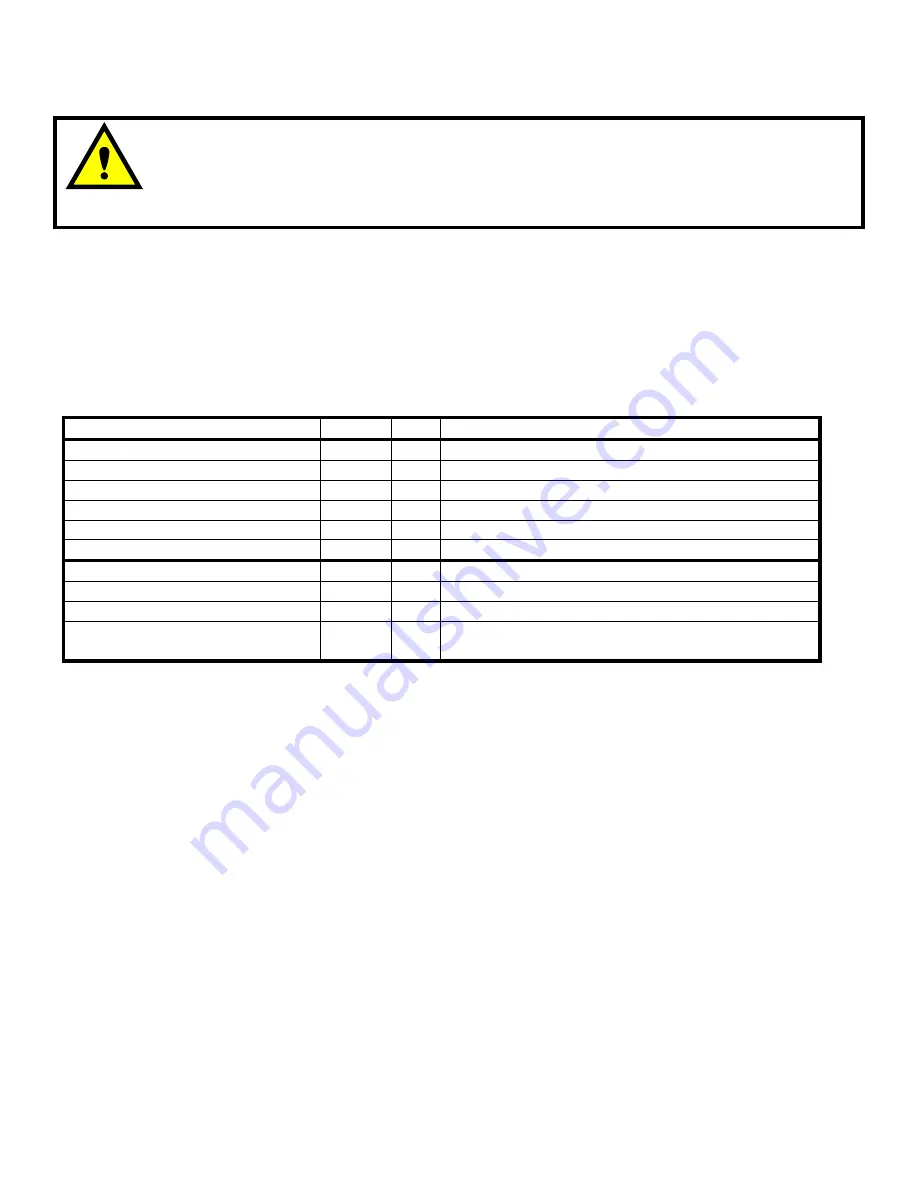

Diagnostic Name

SPN

FMI Meaning

Input 1 Range Low

6370

1

Input signal Below Minimum Range

Input 1 Range High

6371

0

Input signal Above Maximum Range

Output 1 Open Circuit

6372

5

Current Below Normal or Open Circuit

Output 1 Over Current

6373

6

Current Above Normal or Grounded Circuit

Output 2 Open Circuit

6374

5

Current Below Normal or Open Circuit

Output 2 Over Current

6375

6

Current Above Normal or Grounded Circuit

Power Supply Undervoltage

168

4

Voltage Below Normal or Shorted to Low Source

Power Supply Overvoltage

168

3

Voltage Above Normal or Shorted to High Source

Flash Checksum Error

8621

31

Condition Exists

Lockstep, Flash ECC, RAM ECC

Single-bit, Double-bit Error

629

2

Data Erratic, Intermittent or Incorrect

In the case of Lockstep / Flash ECC / RAM ECC Single- and Double-bit Error faults; these faults

are triggered by

internal computations within the microcontroller’s dual core. The entire Flash

where the firmware resides is calculated with ECC (Error Correction Code). If there is any

discrepancy in data in this Flash area, then a fault is triggered. Similarly, the RAM is also

calculated with ECC to ensure data allocated is properly managed. Any discrepancy will trigger a

fault. With respect to Lockstep error detection, both cores of TMS570LS0714 are running in

parallel and validating each other. If there is any single- or double-bit fault discrepancy between

both cores then a fault is triggered. Any of these faults will trigger a DM1 with SPN 629 and FMI 2.

1.7. Constant Data

The Constant Data Block contains four configurable constant data setpoints which can be used as

a control source for other functions. While they are available as a control source to all functions, it

is recommended not to use constant data as a control source for the Set-Reset Latch Block or

Global Constant Signals 0/1 could be used.