ZedBoard Booting and Configuration Guide

ISE Design Suite 14.1

7

JTAG Configuration Mode

You can load the FPGA and run the example software application without building the

design by using the demo scripts and the pre-built hardware bitstream and software

application elf files. You must have the Xilinx tools installed on your host, and have the

hardware set up and connected as per the previous steps.

Application Download

1.

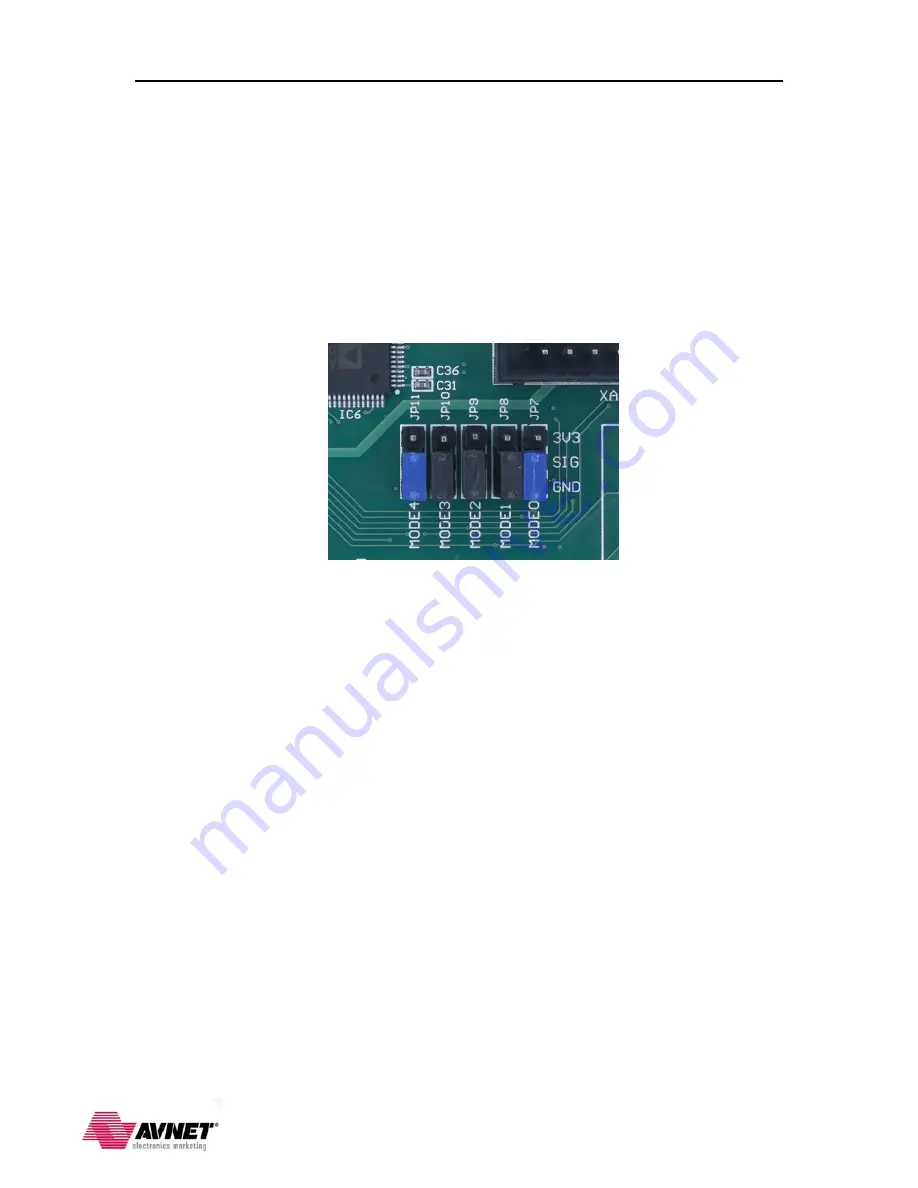

Verify the ZedBoard is powered off and that the configuration Mode jumpers are set

for JTAG mode (all pins shunted to GND) as in the figure below:

2.

Slide the power switch (SW8) to the ON position. You will see the green ‘power

good’ LED (LD13) illuminate.

3.

Navigate to Control Panel

Device Manager

Ports (COM & LPT) and identify

the COM port connected to the ZedBoard. Start a serial terminal session for the

identified COM port and set the serial port parameters to

115200

baud rate,

no

parity,

8

bits,

1

stop bit and no flow control.

4.

Open a command window in the

<installation>\demo

folder and enter:

run_gpio_test.bat

This batch file sets the proper environment variables and creates the xmd.ini script of

commands to be used by the Xilinx Microprocessor Debugger (XMD) tool to

program the PL bitstream, initialize the processor, download the application code, and

begin execution on the system by performing the following commands automatically:

source load_bits.tcl

connect arm hw

source ps7_init.tcl

ps7_init

dow gpio_test_0.elf

run

exit