76

4317I–AVR–01/08

AT90PWM2/3/2B/3B

XCK, USART External clock. The Data Direction Register (DDD0) controls whether the clock is

output (DDD0 set) or input (DDD0 cleared). The XCK0 pin is active only when the USART oper-

ates in Synchronous mode.

SS_A: Slave Port Select input. When the SPI is enabled as a slave, this pin is configured as an

input regardless of the setting of DDD0. As a slave, the SPI is activated when this pin is driven

low. When the SPI is enabled as a master, the data direction of this pin is controlled by DDD0.

When the pin is forced to be an input, the pull-up can still be controlled by the PORTD0 bit.

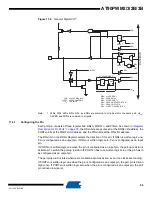

relates the alternate functions of Port D to the overriding signals

shown in

Table 11-10. Overriding Signals for Alternate Functions PD7..PD4

Signal Name

PD7/

ACMP0

PD6/ADC3/

ACMPM/INT0

PD5/ADC2/

ACMP2

PD4/ADC1/RXD/

ICP1A/SCK_A

PUOE

0

0

0

RXEN + SPE •

MSTR • SPIPS

PUOV

0

0

0

PD4 •

PUD

DDOE

0

0

0

RXEN + SPE •

MSTR • SPIPS

DDOV

0

0

0

0

PVOE

0

0

0

SPE • MSTR •

SPIPS

PVOV

0

0

0

–

DIEOE

ACMP0D

ADC3D + In0en

ADC2D

ADC1D

DIEOV

0

In0en

0

0

DI

–

INT0

ICP1A

AIO

ACOMP0

ADC3

ACMPM

ADC2

ACOMP2

ADC1