UG-1462

User Guide

Rev. 0 | Page 4 of 18

EVALUATION BOARD HARDWARE

The EVAL-ADGM1004SDZ evaluation kit contains a fully fitted

printed circuit board (PCB).

The EVAL-ADGM1004SDZ allows the RF signals to connect to

the MEMS switch. Control the switch operation either by using

the on-board links or by applying the correct control signals to

the appropriate connectors.

The EVAL-ADGM1004SDZ provides an additional transmission

line to facilitate the calibration of the network analyzer, which

minimizes the effects of the PCB tracks that connect the RF signals

to the MEMS switch. The calibration process is described in the

Network Analyzer Calibration Procedure section.

POWER SUPPLY

To operate the EVAL-ADGM1004SDZ, provide an external power

supply connected to the P5 power block. The supply voltage is

3.3 V, and must be positive with respect to the ground of the PCB.

The ground of the PCB is marked as GND on the silkscreen (see

Figure 18).

RF CONNECTORS

The RF1 to RF4, and RFC Subminiature Version A (SMA) edge

connectors on the EVAL-ADGM1004SDZ connect to each

switch on the

for performance evaluation purposes.

The RF5 and RF6 connectors connect to a transmission line to

estimate the loss associated with the PCB (see the Measuring

Switch Performance section). Table 1 describes the RF

connectors on the

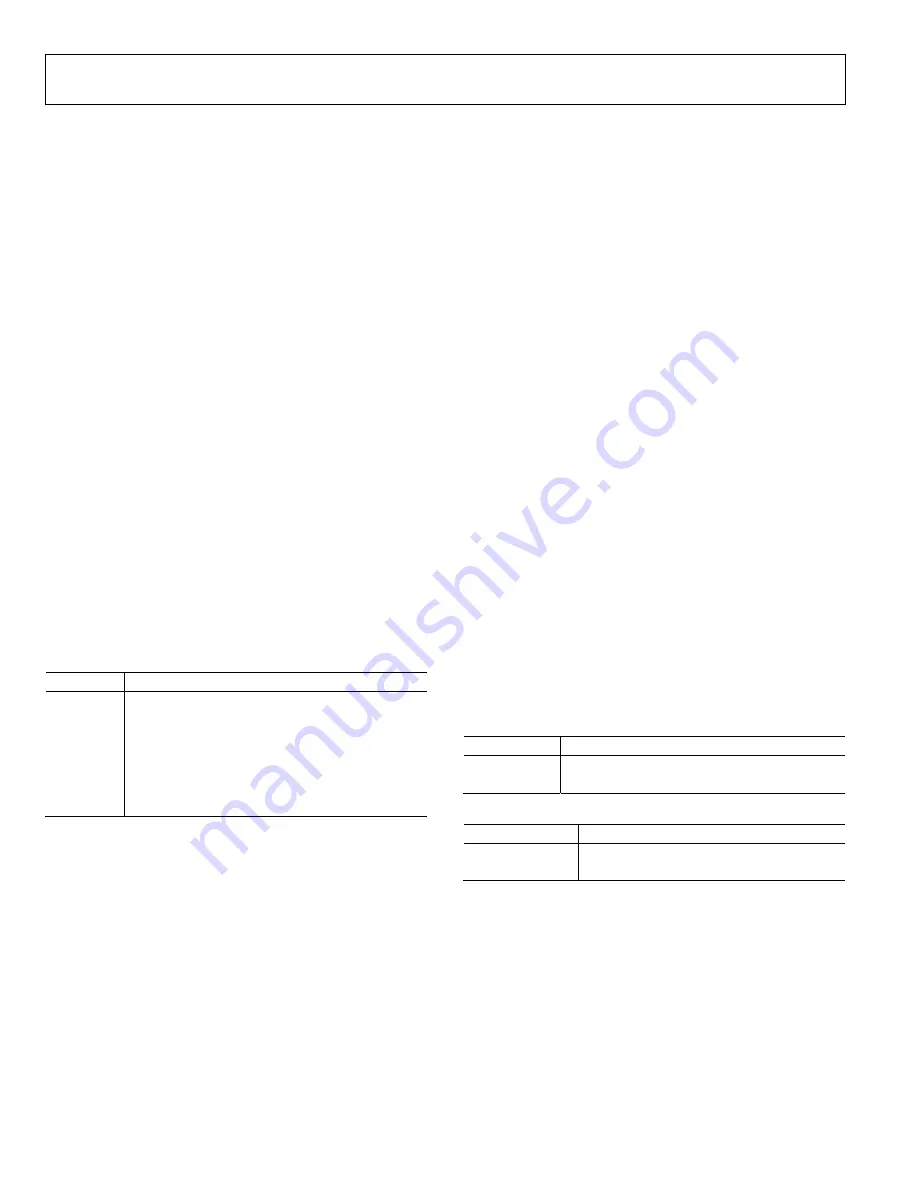

RF Connectors

Connector Description

RFC

Common RF port of the

RF1

Port RF1 of the

RF2

Port RF2 of the

RF3

Port RF3 of the

RF4

Port RF4 of the

RF5, RF6

CALIBRATION THRU calibration transmission lines

used for calibration

SWITCH CONTROL CONNECTORS

The internal control IC co-packaged with the MEMS switch

generates the voltage required to drive the switch. The control

IC generates a reference clock signal at 10 MHz. In normal

operation, set the EXTD_EN link to the INT position to allow

the built in, 10 MHz oscillator to enable the internal driver IC

voltage boost circuitry. Setting the EXTD_EN link to the EXT

position disables the internal 10 MHz oscillator and driver boost

circuitry. Disabling the internal oscillator eliminates the associated

10 MHz noise feedthrough from the switch. With the internal

oscillator disabled, the VCP pin must be driven with 80 V dc

from an external voltage supply. An external 80 V dc must be

applied at the EXT_VCP SMB connector located on the EVAL-

ADGM1004SDZ. With the oscillator disabled, the switch can be

controlled by parallel logic interface (as shown in Table 4) or via

the SPI. With the internal oscillator disabled, the ADGM1004

only consumes a 50 μA maximum supply current.

R10 to R16 are the place holder locations for the 10 MΩ shunt

resistors, which can be placed on all RFx pins (RF1 to RF4, and

RFC) to avoid floating nodes. For more details, see the ADGM1004

data sheet.

comes with a standard LVTTL parallel

interface consisting of four input pins (Pin IN1 to Pin IN4)

which are controlled by the IN1 to IN4 links. See Table 4 for

more details on the logic control when using the parallel interface.

The

also has an SPI interface, which the P1 to P4 links

control. Set the MODE link to the SPI position to enable the SPI

interface. Set the MODE link to the PIN position to enable

parallel interface (see Table 2

.

Table 2. MODE Link Position

Position

Reference Clock Setting

PIN (Default)

Enables parallel interface

SPI

Enables SPI interface, disables parallel interface

Table 3. EXTD_EN Link Position

Position

Reference Clock Setting

INT (Default)

Enables built in 10 MHz oscillator

EXT

Disables the internal oscillator

RFx to RFC Switch Control

The IN1 to IN4 input pins control the switch state and operation

mode of the

in parallel interface mode. The EVAL-

ADGM1004SDZ allows the user to control these pins by using

the IN1 to IN4 and P1 to P4 links (see Table 4), or by applying

external signals to the IN1 to IN4 SMB connectors when in

parallel interface mode. To apply external digital signals to the

IN1 to IN4 links via the SMA connectors, headers must be

removed to leave the IN1 to IN4 links floating.