UG-901

EVAL-AD7175-8SDZ User Guide

Rev. 0 | Page 6 of 10

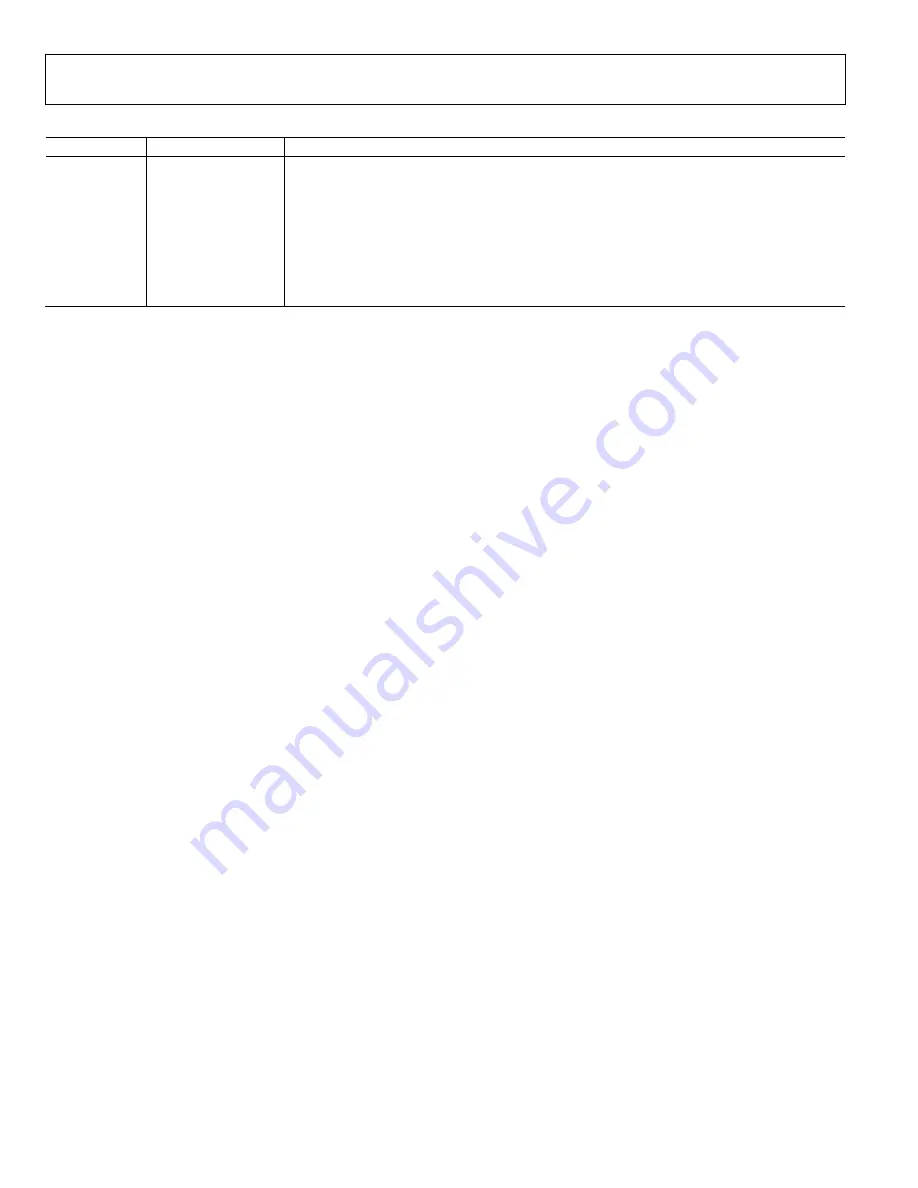

Table 3. Power Supply Configurations

1

Configuration Input Voltage Range

Description

Single Supply

(Regulated)

7 V to 9 V

The 7 V to 9 V input is regulated to 5 V for AVDD1/AVDD2 and 3.3 V for IOVDD. This supply also

powers the external 5 V reference. See the Single Supply (Regulated) section.

Single Supply

(Unregulated)

7 V to 9 V, 5 V, and

3.3 V

The input is unregulated and connects directly to AVDD1/AVDD2 and IOVDD from J5. The 7 V to

9 V input powers the external 5 V reference. See the Single Supply (Unregulated) section .

Split Supply

(Regulated)

7 V to 9 V and −2.5 V

The 7 V to 9 V input is regulated to 2.5 V for AVDD1/AVDD2 and 3.3 V for IOVDD. The 7 V to 9 V input

powers the external 5 V reference, and the −2.5 V input is connected to AVSS directly (unregulated).

See the Split Supply (Regulated) section.

Split Supply

(Unregulated)

7 V to 9 V, ±2.5 V,

and 3.3 V

The input is unregulated and connects directly to AVDD1/AVDD2 and IOVDD from J5. The 7 V to

9 V input powers the external 5 V reference. See the Split Supply (Unregulated) section.

1

Only one configuration can be used at a time.

POWER SUPPLY CONFIGURATIONS

Single Supply (Regulated)

There are two available power supply options for the single-

supply (regulated) configuration.

•

An ac-to-dc adapter (included) connected to J4. Set LK2 to

Position B.

•

A bench top power supply connected to J3. Set LK2 to

Position A and ensure that AVSS = AGND = 0 V.

Set all other links and solder links to the default settings as

outlined in Table 1.

Single Supply (Unregulated)

To set up the board, use the following procedure:

1.

Move SL5 to Position A and SL7 to Position B.

2.

Connect the two terminals of J5 labeled AGND and AVSS.

3.

Connect 0 V (GND) to J5 at the terminal labeled AGND.

4.

Connect 5 V to J5 at the terminal labeled AVDD.

5.

Connect 3.3 V to J5 at the terminal labeled IOVDD.

6.

Connect the 7 V to 9 V input to either J3 or J4.

Set all other links and solder links to the default settings as

outlined in Table 1.

Split Supply (Regulated)

To set up the board, use the following procedure:

1.

Remove SL12 to SL15. These links connect AVSS to AGND.

2.

Connect a bench top power supply to J3 and set LK2 to

Position A. Make sure that AVSS = −2.5 V in this case.

3.

Set LK1 to Position B. This sets the input to the power

monitor circuitry to work with the lower AVDD1 supply

of 2.5 V.

Set all other links and solder links to the default settings as

outlined in Table 1.

Split Supply (Unregulated)

To set up the board, use the following procedure:

1.

Move SL5 to Position A and move SL7 to Position B.

2.

Remove SL12 to SL15.

3.

Connect 0 V (GND) to J5 at the terminal labeled AGND.

4.

Connect 2.5 V to J5 at the terminal labeled AVDD.

5.

Connect −2.5 V to J5 at the terminal labeled AVSS.

6.

Connect 3.3 V to J5 at the terminal labeled IOVDD.

7.

Connect 7 V to 9 V to either J3 or J4. Connect or disconnect

the AVSS terminal of J3 to the AVSS terminal of J5.

8.

Set LK1 to Position B. This sets the input to the power moni-

tor circuitry to work with the lower AVDD1 supply of 2.5 V.

Set all other links and solder links set to the default settings as

outlined in Table 1.

ANALOG INPUTS

primary analog inputs can be applied

in two separate ways:

•

J10, J12, and J14 connectors on the left side of the board

•

A0 to A3 SMB/SMA footprints on the evaluation board

The analog inputs route directly to the associated analog input

pins on the

, provided that the LK5 to LK20 links

(on-board noise test) are removed. The

evaluation

software is set up to analyze dc inputs to the ADC. The

input buffers work for dc input signals.

REFERENCE OPTIONS

includes an external 5 V reference,

the

. The

includes an internal 2.5 V reference.

The default operation is to use the external reference input,

which is set to accept the 5 V

on the evaluation board.

Choose the reference in the SETUPCONx registers associated

with Setup 0 to Setup 7 to select the reference used for

conversions by the

Change between the internal and external references by

accessing the

register map in the evaluation software

(click

ADC Setup

).